Verification IP

Avery Verification IP (VIP) plays a crucial role in ensuring the success of complex semiconductor designs by offering a wide range of benefits and a compelling value proposition. Avery Verification IP provides pre-verified and reusable components, tools, and methodologies that enable efficient and thorough verification of electronic designs.

-

On-Demand

Shift-Left Compute Subsystem RTL Sign-Off with Software Aware VIP

In this webinar, we present a scalable methodology to accelerate the development and verification of Compute Subsystems such as Arm® Neoverse™ V3 Compute Subsystem (CSS)-based designs, with a shift-left in simulation and signoff using Avery Protocol VIP, CSS VIP, Software Aware VIP, Arm Fast Models and QEMU models.

-

On-Demand

Securing Next-Generation Interconnects: PCIe® Gen7 Security Verification

This webinar highlights what’s new in PCIe Gen7 security and demonstrates how Avery Verification IP-built on deep PCIe and UCIe verification expertise-enables early validation of TDISP and IDE functionality, comprehensive protocol and security coverage, and faster compliance, reducing risk and time-to-market for secure PCIe designs.

-

Verification Protocols & Support

Questa One Avery Verification IP improves quality and reduces schedule times by building protocol and methodology reusable components that support many industry standard interfaces and memories.

-

Avery Verification IP Sessions

-

Shift-Left Compute Subsystem RTL Sign-Off with Software Aware VIP

In this webinar we present a scalable methodology to accelerate the development and verification of Compute Subsystems such as Arm® Neoverse™ V3 Compute Subsystem (CSS)-based designs, with a shift-left in simulation and signoff using Avery Protocol VIP, CSS VIP, Software Aware VIP, Arm Fast Models and QEMU models. -

Securing Next-Generation Interconnects: PCIe® Gen7 Security Verification

This session highlights what’s new in PCIe Gen7 security and demonstrates how Avery Verification IP-built on deep PCIe and UCIe verification expertise-enables early validation of TDISP and IDE functionality, comprehensive protocol and security coverage, and faster compliance, reducing risk and time-to-market for secure PCIe designs. -

Ultra Accelerator Link (UALink) Verification: A Deep Dive with Siemens Avery Verification IP

In this webinar, you will be introduced to the UALink protocol, focusing on its architecture, key features that enable scalable AI systems, and critical verification challenges. We will then explore the essential capabilities of Siemens Avery UALink Verification IP, designed to ensure complete and efficient verification of complex UALink-based accelerator designs. -

Breaking Barriers: Ethernet 1.6T, Infiniband, UALink, and UEC Verification for Next-Gen Connectivity

This session introduces Avery Verification IP for Ethernet 1.6T, Infiniband, UALink, and UEC, providing essential tools to verify complex designs for next-generation connectivity. You will gain insights into the key challenges and innovations in Ethernet 1.6T, the latest high-speed Ethernet standard, and learn how Avery's Verification IP accelerates design validation with comprehensive protocol coverage, scalability, and advanced debugging capabilities. -

Verifying the Next Generation High Bandwidth Memory Controllers for AI and HPC Applications

In this session, you will learn how Siemens’s scalable and customizable Avery HBM Verification IP helps companies like Rambus verify their industry-leading HBM4 Controller IP through rigorous testing to ensure reliability and performance. -

The Future of Multi-Die System Verification with UCIe

In this session, you will be introduced to the UCIe protocol with a focus on the latest evolutions of the specification, followed by a deep dive into the key features of Siemens Avery UCIe Verification IP that enable efficient verification of multi-die systems. These include dynamic block-level and System-in-Package (SiP) level testbench creation, intelligent traffic generation, error injection, advanced debug features, and comprehensive performance monitoring. -

Accelerated Confidence in Interface Designs Mixing Software Layers, Hardware Protocols, Physical Connections

In this session, you will learn that today high performance compute fabrics are spread over multiple die, multiple packages, multiple cards and racks in the data center. They are linked together by layers of CPU-to-CPU, cache-to-cache, and network node-to-node infrastructure. Those connections are based on standardized protocols, always evolving and improving, and increasingly having both a hardware interaction of multiple layers, plus one or more software layers. -

How We Use PCIe Verification IP Across Multiple Projects

In this session we will discuss how Marvell delivers successful products and drives the market by with a structured design and verification methodology that reflects this philosophy. Specifically, we will dive deep into one of the most complex protocols: PCIe IP and the related testbench architecture; and how we adopted Siemens’ PCIe Avery Verification IP. -

Reduce Gate-level Simulation Bring-up Time with Semi-formal X Verification

This session will describe a reliable formal-based method to manage Xs in GLS. It centers on the use of Siemens Avery SimXACT solution alongside your preferred simulator. -

Comprehensive CXL 3.0 Verification for High-Bandwidth and Low-Latency Connectivity

In this session, you will learn considerations for exhaustive verification of the CXL interconnect and how the Siemens Avery CXL Validation Suite enables hardware and software development teams to start system integration and validation extremely early. -

Comprehensive PCIe Verification for Bleeding Edge and Mission Critical SoC & IP Designs

In this session, you will learn design considerations for PCIe 5.0 and 6.0 design IP and how you can stay ahead in the market in verifying the most advanced and critical features of PCIe 6.0 and 5.0 for your design IPs. -

Multi-Die System Verification with UCIe Avery Verification IP

In this session, we will introduce you to Siemens EDA's Verification Portfolio and then deep dive into UCIe Verification IP, discussing its key features such as dynamic block-level and SoC level testbench creation, traffic generation, error injection, debug features, and performance monitoring. Siemens Avery UCIe Verification IP is a leading solution in the market, runs on all major simulators and is a native SystemVerilog/UVM class-based Verification IP. -

Delivering First Silicon Success for Your Next SoC or 3DIC

In this session, you will learn about the protocol and memory verification solutions needed for your next silicon verification project whether in Datacenter, Storage, 3DIC, Networking, Automotive or Mil/Aero applications.

-

-

Verification IP Forum Discussion

-

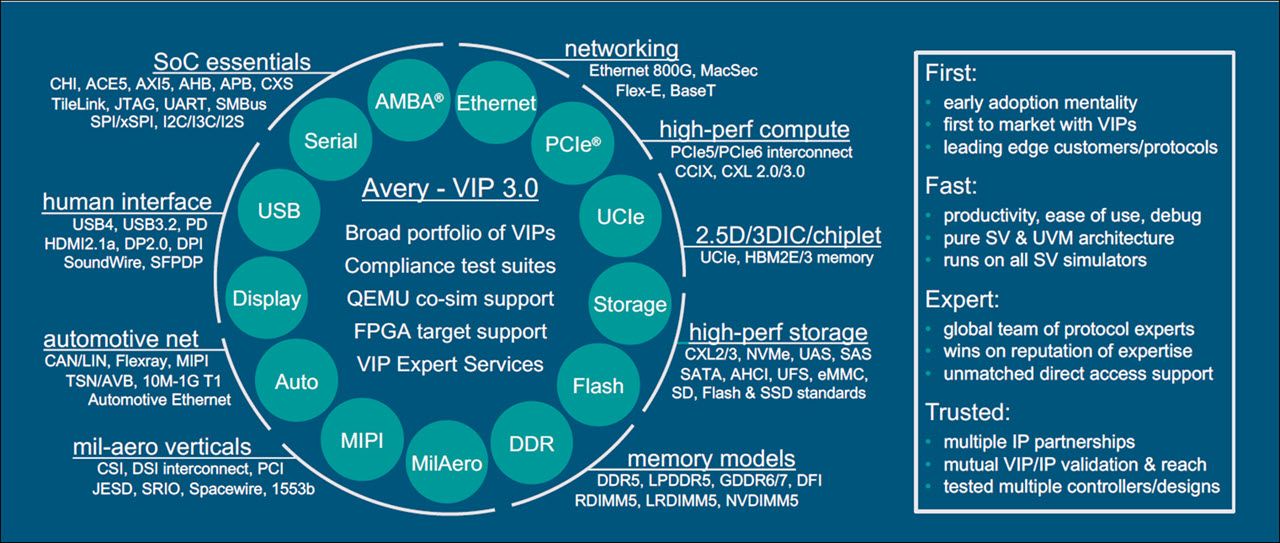

VIP Block Container Primary (Overview)

-

Verification IP Enhances Productivity

Avery Verification IP Enhances Productivity

Avery Verification IP (VIP) offers a comprehensive solution to address the challenges faced by semiconductor design and verification teams. It provides pre-built, reusable verification components that represent various protocols, interfaces, and standards used in modern electronic systems. Avery Verification IP includes models, testbenches, assertions, and coverage models specific to each protocol, enabling faster and more effective verification of complex designs. By leveraging Avery Verification IP, design and verification teams can significantly reduce the time and effort required to develop custom verification environments, thus accelerating the overall verification process.

One of the key value propositions of using Avery Verification IP is its ability to enhance productivity. Avery Verification IP eliminates the need for design and verification teams to develop verification components from scratch for each design project. Instead, they can leverage pre-verified and reusable Avery Verification IP components, which saves considerable time and effort. This allows engineers to focus on higher-value tasks such as critical corner-case scenarios and system-level verification, resulting in increased productivity and improved time-to-market.

Moreover, Avery Verification IP offers a higher level of confidence in the design correctness. Avery Verification IP vendors invest significant resources in developing and rigorously testing their verification components, ensuring their reliability and accuracy. These components undergo extensive verification against protocol specifications, stress testing, and compatibility checks, thus minimizing the risk of undetected bugs and functional issues. By utilizing Avery Verification IP, design teams can leverage the expertise and experience of the Avery Verification IP vendor, ultimately leading to higher-quality designs and reducing the chances of costly re-spins.

Another benefit of using Avery Verification IP is its ability to enable comprehensive verification. Avery Verification IP includes a wide range of features such as error injection, protocol checking, and coverage analysis, which facilitate thorough and exhaustive verification. With Avery Verification IP, engineers can easily validate the compliance of their designs with specific protocols and standards, ensuring interoperability and compatibility with other components. Avery Verification IP also provides advanced features like functional coverage and transaction-level modeling, enabling a deeper analysis of system-level behavior and verification closure.

Reusability and Interoperability

Avery Verification IP is designed to be highly reusable across different projects and teams. Once an Avery Verification IP is developed and validated, it can be reused in multiple projects, saving time and effort. Moreover, Avery Verification IPs from different vendors are often interoperable, allowing engineers to mix and match components from different sources. This interoperability enables collaboration between different teams and facilitates the exchange of verification components, further increasing productivity.

Faster Time-to-Market

Verification is a critical aspect of the design process that can significantly impact time-to-market. By using Avery Verification IP, engineers can accelerate the verification process, identify and resolve issues earlier, and reduce the overall time required for verification. Avery Verification IPs provide a head start in developing verification environments, allowing engineers to focus on the unique aspects of their designs and quickly iterate through the verification process. This shortened verification cycle translates into faster time-to-market, giving companies a competitive edge.

Risk Mitigation

Avery Verification IP helps mitigate risks associated with complex designs. By relying on pre-verified Avery Verification IPs, engineers can detect and fix design issues early in the development cycle. This reduces the risk of costly re-spins and improves overall design quality. Avery Verification IPs also provide comprehensive error detection and coverage analysis capabilities, allowing engineers to identify potential corner cases and ensure robustness in their designs. By using Avery Verification IPs, companies can mitigate risks associated with verification and improve the overall reliability of their products.

Cost Savings

Developing and maintaining in-house verification environments for complex protocols can be expensive. Avery Verification IP offers a cost-effective solution by providing pre-verified and reusable models. Instead of investing resources in developing and maintaining protocol-specific verification environments, companies can leverage Avery Verification IPs to save time, effort, and costs. Additionally, the reusability and interoperability of Avery Verification IPs further contribute to cost savings by maximizing the utilization of existing verification assets across different projects.

Comprehensive Protocol Support

Avery Verification IP offers comprehensive protocol support for widely used industry standards such as PCIe, USB, Ethernet, HDMI, AMBA, and many more. These protocols are constantly evolving, and developing verification environments from scratch for each new protocol version can be time-consuming and error-prone. Avery Verification IPs keep pace with the latest protocol specifications, ensuring accurate and up-to-date verification. This allows engineers to focus on the unique aspects of their design, rather than spending time on protocol-specific details.

Accurate and Reliable Verification

Avery Verification IP is developed by experts who have an in-depth understanding of the protocols they represent. These experts work closely with the standardization bodies and contribute to the development and refinement of protocol specifications. Avery Verification IPs undergo rigorous testing and verification, ensuring accuracy and reliability. By using Avery Verification IPs, engineers can have confidence in the correctness of their verification environment and focus on identifying design issues rather than worrying about potential protocol bugs.

Improved Verification Productivity

Avery Verification IP significantly enhances the productivity of verification engineers by providing pre-verified and reusable models for standard protocols and interfaces. Instead of starting from scratch, engineers can leverage these models to accelerate the verification process. Avery Verification IPs encapsulate the knowledge and expertise of protocol specifications, reducing the effort required to understand complex protocols and accelerating the development of verification environments.

Avery Verification IP Conclusion

Avery Verification IP fosters collaboration and compatibility among different design and verification teams. As Avery Verification IP components are standardized and widely adopted in the industry, they serve as a common language between various teams working on different parts of a complex design. This ensures seamless integration and communication, leading to improved overall project efficiency. Avery Verification IP also enables the reuse of verification environments across different projects and teams, fostering a scalable and modular approach to verification methodology.

Cost savings is another significant advantage offered by Avery Verification IP. Developing custom verification components requires substantial engineering resources, including skilled personnel, time, and infrastructure. By utilizing Avery Verification IP, design teams can avoid these costs, as the pre-built components are already available and extensively tested. Additionally, Avery Verification IP reduces the risk of missed bugs and design issues, which can result in expensive re-spins and delays. By investing in high-quality Avery Verification IP, companies can achieve significant cost savings throughout the entire design and verification process.

In conclusion, the value proposition and benefits of using Avery Verification IP are extensive. Avery Verification IP enhances productivity, improves design correctness, enables comprehensive verification, fosters collaboration, and offers cost savings. With Avery Verification IP, design and verification teams can leverage pre-verified and reusable components, saving time and effort while ensuring high-quality designs. As the complexity of electronic systems continues to grow, Avery Verification IP plays a critical role in accelerating the verification process, reducing risk, and ultimately enabling successful semiconductor designs.

-