Verifying the Evolving UCIe Landscape: A 3.0-Aware Architecture for Manageability and Beyond

This white paper details a verification strategy for UCIe 3.0 designs, integrating both legacy manageability architecture and emerging UCIe 3.0 features into a reusable, scalable framework. Built on a layered UVM architecture, Questa One™ Avery™ VIP for UCIe enables flexible modeling of complex domains through configurable APIs and supports automated discovery and routing table set up for both direct and indirect management paths.

-

Introduction

The Universal Chiplet Interconnect Express™ (UCIe) standard is revolutionizing system-in-package (SiP) design by enabling scalable integration of heterogeneous chiplets across vendors. It has rapidly evolved as the de facto standard for integrating heterogeneous chiplets into unified SiPs.

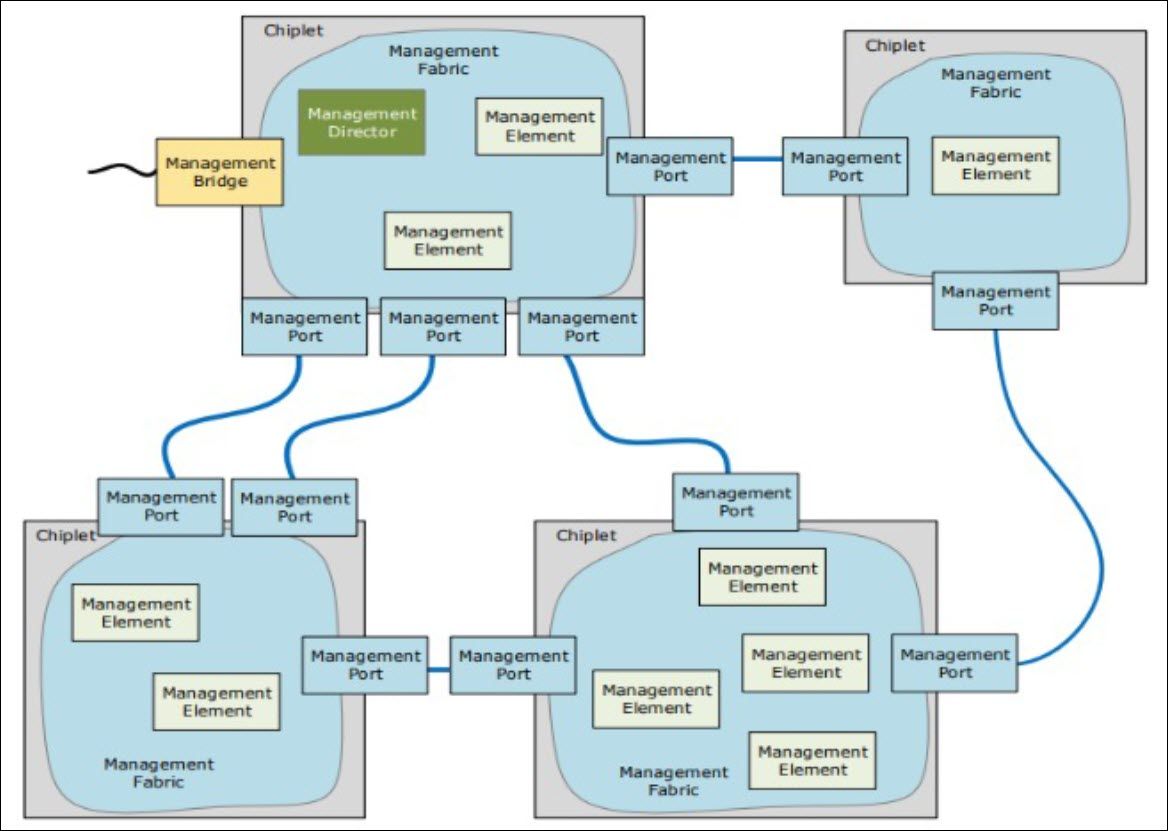

A central pillar of UCIe 2.0 is its manageability architecture, which introduced a structured control plane that enables configuration, communication, and monitoring between distributed management entities embedded in chiplets. This architecture defines a hierarchical model composed of management elements, management ports, and port gateways, which govern the flow of management transport packets (MTP). These packets are exchanged over sideband or mainband links and must adhere to encapsulation, flow control, and routing rules that vary with link type and topology.

Verification of such systems presents non-trivial challenges: dynamic discovery and initialization of the management domain, encapsulation into UCIe transport frames, complex routing through direct and indirect paths, and across hierarchical chiplet domains, strict adherence to transmitter and receiver rules for interleaving, segmentation and ordering in multi-stack and multi-module configurations, support for diverse management protocols and security-enforced access control. Thus, the addition of this manageability fundamentally expands the scope of verification, bringing dynamic behavior such as discovery, initialization, access control enforcement, multi-hop routing, and protocol-specific payload decoding into the simulation space—all of which must be rigorously validated across varying configurations.

Figure 1: SiP that supports manageability

UCIe 3.0: Feature Upgrades and Additions

With the release of UCIe 3.0, the specification expands support for next-generation performance and robustness. While UCIe 2.0 introduced the manageability architecture, UCIe 3.0 pushes the envelope with performance-driven and system-level enhancements that directly affect verification demands.

Key additions include:

- 48 GT/s and 64 GT/s data rates that stress signal integrity and timing across the interconnect

- Runtime link recalibration requiring adaptive validation under live traffic conditions

- Priority sideband transport that bypasses normal negotiation flows

- Sideband power down for L2

- Circular buffer-based transport that alters MTP flow control

- Early firmware downloads triggering management sequences ahead of full link bring-up

- Open drain signaling, emergency shutdown, and fast-throttle provide power-aware system control

These capabilities build on the UCIe 2.0 model requiring backward-compatible manageability flows—like discovery, routing, and encapsulation—to be verified under new constraints and concurrent scenarios. For example, the manageability flow must function correctly even when lanes are recalibrating in the background or when priority packets are taking precedence on sideband paths.

This paper proposes a verification architecture combining the depth of UCIe 2.0 manageability validation along with next-generation UCIe 3.0 features in realistic multi-die environments.

-

Download Paper

-

Verifying the Evolving UCIe Landscape: A 3.0-Aware Architecture for Manageability and Beyond

Verification IP Aug 13, 2025 pdf

-