Verification Academy Live Hudson

This seminar will provide design engineers and verification teams with the knowledge and tools needed to advance their workflows using the latest AI-driven automation, intelligent verification platforms, and industry-proven methodologies.

Tuesday, June 9, 2026 | 9:00 AM - 5:00 PM

Location

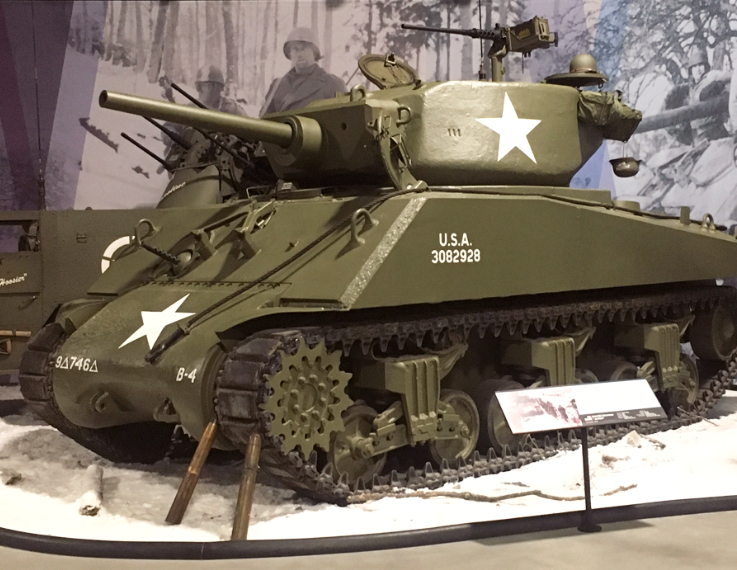

American Heritage Museum

568 Main St

Hudson, MA 01749

+1 (978) 562-9182

This event is in-person only — there is no support for remote participation.

-

Event Description

Specifically, we will cover:

- How generative AI and agentic automation are transforming chip design, RTL development, and verification closure workflows.

- The latest advancements in Verification IP (VIP) for accelerating interface-level verification and bridging hardware and embedded software validation.

- How to protect against data corruption and strengthen hardware security posture using formal security verification techniques.

- How AI/ML-driven Verification IQ (VIQ) delivers predictive insights, coverage guidance, and regression optimization for smarter, faster verification closure.

-

Agenda

Details Time REGISTRATION AND CHECK-IN

Coffee and networking with your peers.

9:00 AM – 9:30 AM WELCOME AND INTRODUCTION

Todd Holbrook | Siemens

9:30 AM – 9:45 AM GENERATIVE AI FOR CHIP DESIGN

Ronen Shoham | Siemens

This session explores Questa One Agentic Flows, showcasing how AI-driven automation is transforming both simulation and formal verification workflows. We will dive into how engineers can leverage intelligent agents to streamline traditionally manual and iterative tasks across RTL development, assertion creation, and verification closure. Attendees will earn how to leverage AI to automate RTL & SVA generation, fix issues identified by Lint and CDC, and automate simulation/formal tasks and works.

o Questa One Agentic Tool Kit

o Lint and CDC Autofix

o RTL Assist

o Property Assist

9:45 AM – 10:45 AM QUESTA ONE VIP AND SOFTWARE AWARE VIP

Tzi Yang Shao | Siemens

This presentation will cover how Questa One VIP accelerates interface-level verification with production-ready, protocol-compliant verification IP, while enabling faster bring-up, reuse, and debug across complex environments. It will also highlight Software Aware VIP, which bridges the gap between hardware verification and embedded software validation. Attendees will learn how to validate real software workloads interacting with hardware interfaces earlier in the cycle, improving system-level confidence and reducing late-stage integration risks.

10:45 AM - 11:30 AM FROM ALGORITHM TO UVM: ACCELERATING DESIGN VERIFICATION WITH MATLAB®, SIMULINK®, AND HDL VERIFIER™

Andrew Santos | MathWorks

This session will show how MathWorks tools — MATLAB®, Simulink®, and HDL Verifier™ — enable model-based design techniques to accelerate design verification. Attendees will see how executable reference models and reusable testbench components can be created and run natively in Siemens Questa, enabling shift-left verification across co-simulation, DPI-based testbenches, and UVM/UVM-F environ.

11:30 AM – 12:00 PM COMPLIMENTARY LUNCH AND NETWORKING

12:00 PM – 1:00 PM BAE: AUTOMATION OF FPGA DEVELOPMENT PROCESS USING JENKINS CONTINUOUS INTEGRATION AND CONTINUOUS DEPLOYMENT

Laks Vanchinathan | BAE

This paper presents an implementation of a Continuous Integration/Continuous Deployment (CI/CD) pipeline for FPGA development using Jenkins, an opensource automation server. The CI/CD pipeline automates build, test, and deployment of code changes, standardizing best practices in design and verification workflows.

1:00 PM – 1:30 PM QUESTA ONE SFV TRUST AND ASSURANCE

David Landoll | Siemens

Learn about the effectiveness of enhancing security verification and improving the robustness of hardware security verification through detailed explanations and runtime insights. Explore methods to protect against data corruption using formal security verification techniques.

1:30 PM - 2:30 PM QUESTA ONE VIQ SMART VERIFICATION

Austin Mam | Siemens

This session will explore Verification IQ (VIQ) and how it brings AI/ML-driven intelligence into the verification flow. Attendees will learn how VIQ leverages data from simulation, formal, and coverage to provide actionable insights such as predictive failure analysis, coverage guidance, and regression optimization. By surfacing patterns and prioritizing what matters most, VIQ helps teams focus their efforts whereit drives the greatest impact. The session will demonstrate how smart verification enables improved productivity and a more efficient path to verification closure.

2:30 PM - 3:30 PM RECEPTION

Enjoy appetizers with local sodas and explore the museum.

3:30 PM – 5:00 PM We look forward to seeing you!

Siemens Advanced Functional Verification Team

* The agenda is subject to change without notice. -

Register Here