Standardization of HDMs for Hierarchical CDC and RDC Analysis

Currently HDMs must be generated with the same EDA tool that customers will use to consume the HDM for CDC and RDC analysis at the SoC level. To resolve this problem a CDC Working Group was created within the Accellera organization. The goal of this Working Group is to create a standard format for HDMs so the models can be consumed by any EDA tool irrespective of the source of the generated model.

-

Introduction

In today’s large, complex designs, multiple asynchronous clocks and resets have become the norm. The increase in clock and reset domains is driven by complex SoCs using different controllers to manage more complex power management schemes.

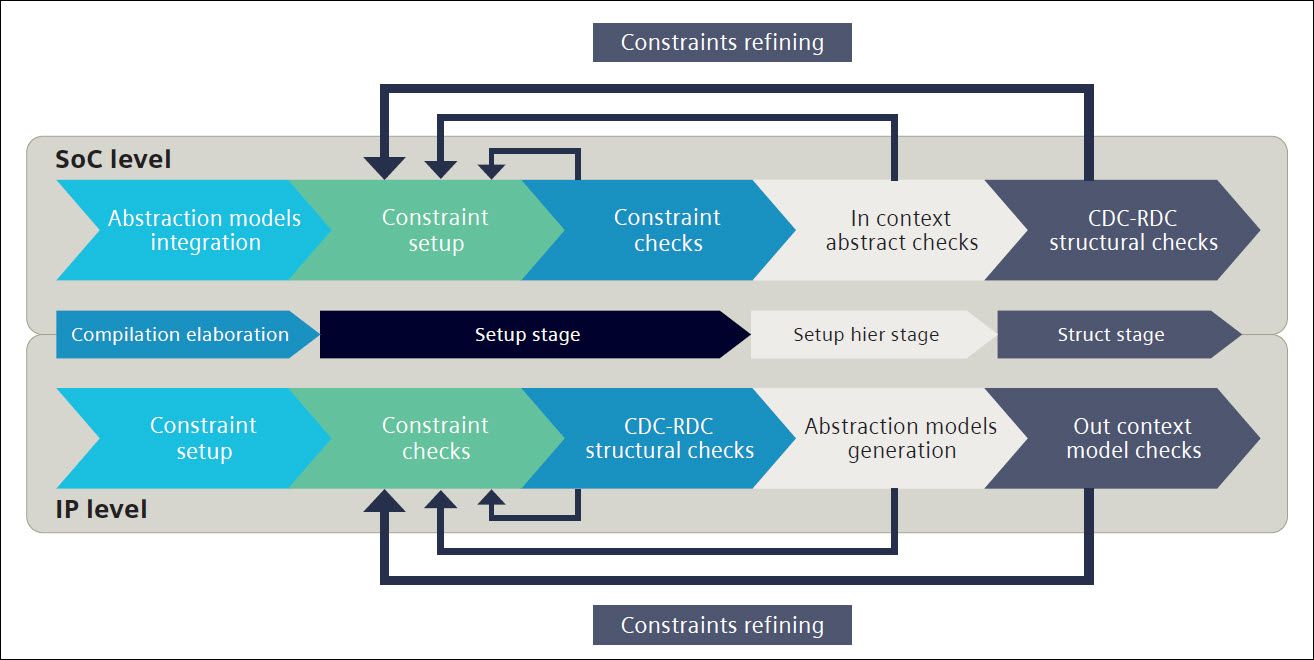

For doing both clock domain crossing (CDC) and reset domain crossing (RDC) analysis on large complex designs, there are several valid reasons why designers prefer to follow a hierarchical data model (HDM) flow:

- Run larger designs faster.

- Reduce noise at block and top levels.

- Ideal for IP-based projects and flows.

- Perform parallel analysis of different blocks to save time.

- Achieve better runtime and memory performance.

- Achieve QoR as good as a flat run.

- Deliver focused results at IP block and top SoC levels.

- IP developers provide abstraction models.

But an HDM flow comes with its own challenges:

- Dependency on sub-block providers to deliver CDC and RDC models.

- Compatibility of CDC/RDC models across multiple EDA tools.

Figure 1: CDC/RDC hierarchical flow.

Creation of Accellera CDC Working Group and Sub-groups

As we move from monolithic designs to IP/SoC, with IP sourced from select providers, sourcing IP globally to create differentiated products becomes a challenge. We must maintain quality as we drive faster time-to-market. In areas where we have standards (SystemVerilog, OVM/UVM, LP/UPF), integration is able to meet both quality and speed. But in areas where we don’t have standards, for example CDC and RDC, most options trade-off either quality or time-to-market or both. Creating a standard for interoperable collateral addresses this gap.

A working group was formed in January 2023 to explore the need for the creation of a standard to converge CDC and RDC collateral integration from different tools and vendors for ease (time-to-market) and quality (bug-free silicon). The Accellera board approved this working group and tasked it to develop a standard format that will be accepted by the semiconductor as well as EDA communities.

-

Download Paper