UVM

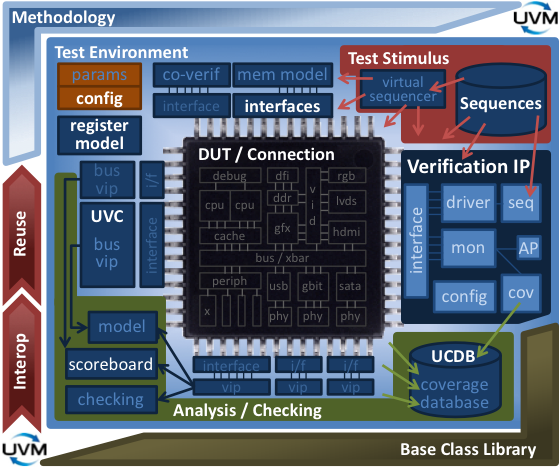

The (2018) version conforms to the IEEE 1800.2 UVM Standard and promotes an emulation-friendly UVM testbench architecture that promotes reuse of your UVM environment as your project moves from simulation to emulation and beyond.

Find all the UVM methodology advice you need in this comprehensive and vast collection.

-

Container Block

-

Introduction

The Accellera UVM standard was built on the principle of cooperation between EDA vendors and customers; this was made possible by the strong foundation of knowledge and experience that was donated to the standardization effort in the form of the existing OVM code base and contributions from VMM.

The result is a hybrid of technologies that originated in Siemens EDA's AVM, Siemens EDA & Cadence's OVM, Verisity's eRM, and Synopsys's VMM-RAL, tried and tested with our respective customers, along with several new technologies such as Resources, TLM2 and Phasing, all developed by Mentor and others to form UVM as we know it.

Combined, these features provide a powerful, flexible technology and methodology to help you create scalable, reusable, and interoperable testbenches. With the OVM at its core, the UVM already embodies years of object-oriented design and methodology experience, all of which can be applied immediately to a UVM project.

-

UVM Mapping

-

-

Introduction

When we commenced work on UVM, Siemens EDA set out to capture documentation of our existing OVM methodology at a fine level of granularity. In the process, we realized that learning a new library and methodology needed to be a dynamic and interactive experience, preferably consumed in small, easily digested spoonfuls.

To reinforce each UVM and OVM concept or best practice, we developed many realistic, focused code examples. The end result is the UVM Online Methodology Cookbook, whose recipes can be adapted and applied in many different ways by our field experts, customers, and partners alike.

As the UVM has continued to be refined in Accellera, we have updated the UVM Cookbook accordingly. This latest update was prompted by the adoption of UVM as IEEE 1800.2 in November, 2017, with the subsequent release by Accellera of a compatible Reference Implementation library shortly thereafter.

The other significant change in the industry since UVM was first introduced is the incredible increase in the size and complexity of designs. What used to be considered a "system" back then is now considered just one piece of a much larger system today. This has greatly increased the demand for faster execution platforms on which to perform verification, and as such we are seeing more and more users adopting emulation, hardware acceleration and FPGA prototyping as part of their functional verification flows.

The requirement to preserve their UVM infrastructure throughout a project has led us to update our recommendation for how to organize a UVM testbench, particularly at the level at which the UVM testbench interacts with the Device under Test (DUT), which you will see throughout this book.

-

Reference Downloads

The UVM Cookbook, related reference implementation, library code and code examples are available for download below.

Cookbook Contents

Introduction

UVM Basics

- Testbench Basics

- UVM Components

- UVM Factory

- UVM Phasing

- UVM Driver

- UVM Monitor

- UVM Agent

- UVM Sequences

- UVM Sequence Items

- UVM Configuration Database

- UVM Packages

UVM Testbench

- Testbench Architecture

- Testbench Build

- Sequence Driver Connection

- Block Level Testbench

- Integration Level Testbench

- Dual Top Architecture

UVM Testbench to DUT Connections

- Connecting the Testbench to the DUT

- Interfaces and Virtual Interfaces

- UVM Configuration Database

- Virtual Interface BFMs

- Handling Parameterization

- Abstract-Concrete Class Connections

- Parameterized Tests

UVM Configuring a Test Environment

- Testbench Configuration

- Configuring Sequences

- Using a Parameter Package

- Accessing Configuration Resources from a Sequence

- Macro Cost-Benefit Analysis

UVM Analysis Components & Techniques

UVM End Of Test Mechanisms

UVM Sequences

- Sequences

- UVM Sequence Items

- Transaction Methods

- Sequence API

- Sequence Driver Connection

- Driver Sequence API

- Generating Stimulus with UVM Sequences

- Overriding Sequences and Sequence Items

- Virtual Sequences

- Virtual Sequencers (Not Recommended)

- Hierarchical Sequences

- The Sequence Library

- Sequence-Driver Use Models

- Unidirectional Protocols

- Bidirectional Protocols

- Pipelined Protocols

- Arbitrating Between Sequences

- Sequence Priority

- Locking or Grabbing a Sequencer

- Slave Sequences (Responders)

- Wait for a Signal

- Interrupt Sequences

- Stopping a Sequence

- Layering Sequences

UVM Messaging System

- Messaging

- Using Messaging

- UVM Report Catcher

- Testing Message Status

- Command-Line Verbosity Control

- Messaging in Sequences

UVM Stimulus Techniques (Other)

UVM Register Abstraction Layer

- Register Package

- Register Model & Structure

- Complex Address Maps

- Specifying Registers

- Register Layer Adapter

- Integrating a UVM Register Model in a Testbench - Overview

- Integrating a UVM Register Model in a Testbench - Implementation

- "Quirky" Registers

- Register Model Coverage

- Backdoor Accesses

- Generating Register Models

- Register-Level Stimulus

- Memory-Level Stimulus

- Register Sequence Examples

- Built-in Register Sequences

- Configuring Registers

- Register-Level Scoreboards

- Register-Level Functional Coverage

UVM Testbench Acceleration through Co-Emulation

- Emulation

- Separate Top-Level Modules

- Split Transactors

- Back Pointers

- Defining an API

- Emulation-Ready Testbench Examples

UVM Debugging

UVM Connect - SystemVerilog/SystemC Interoperability

Appendix - Deployment

Appendix - Coding Guidelines

- SystemVerilog Guidelines

- SystemVerilog Performance Guidelines

- UVM Guidelines

- UVM Performance Guidelines