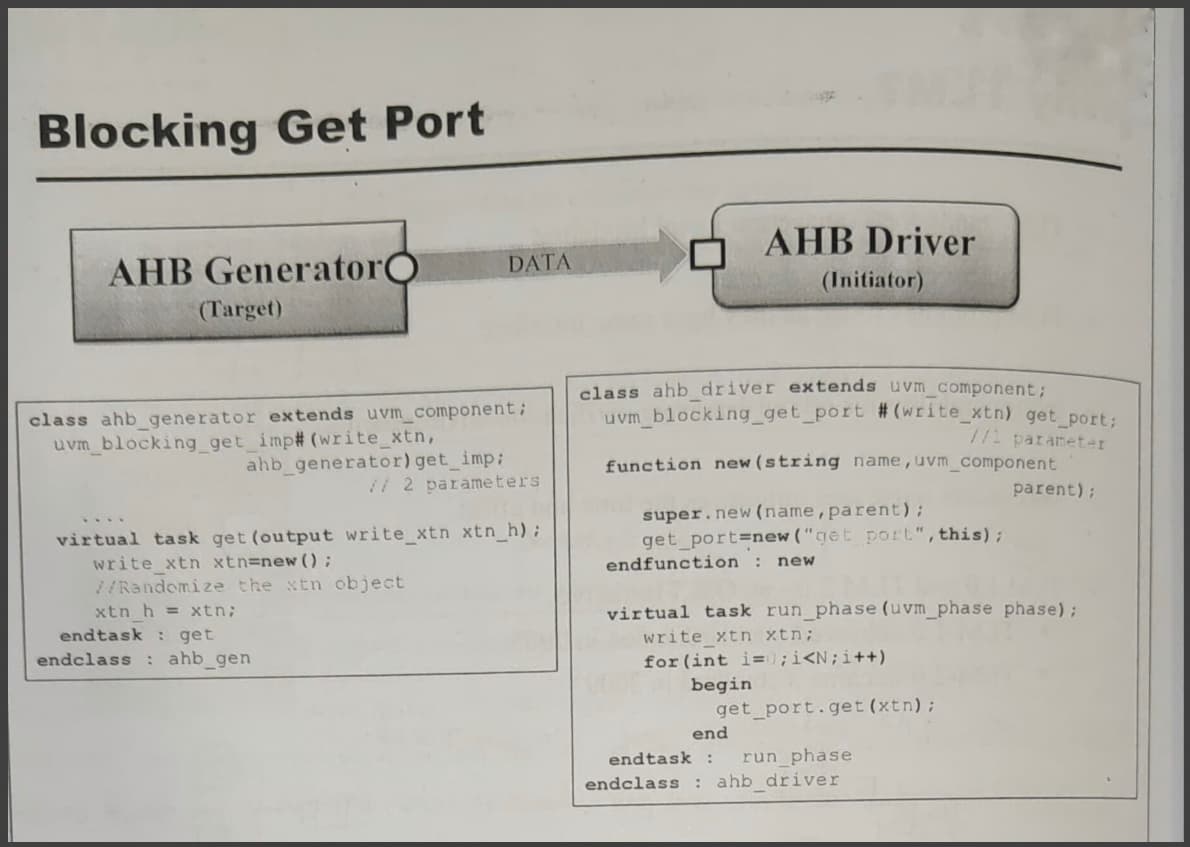

In the diagram below, we make a connection between DRIVER and GENERATOR.

In DRIVER we declared a handle of uvm_blocking_port #(xtn) get_port and in GENERATOR class we declared uvm_blocking_get_imp #(xtn,generator) get_imp ; and also there is a method (task) of get in generator class.

Now if we observe that in driver class we used a handle of uvm_blocking_port class of get_port how we are getting the GET method which is there in Generator class by using other class handle.

explain me how internally it is giving access to driver class GET task

When the driver calls get_port.get() how does this call reach the get() task in the generator, even though get_port is of type uvm_blocking_get_port (a different class)? @dave_59 @chr_sue