Free Yourself from the Tyranny of Power State Tables with Incrementally Refinable UPF

Since UPF was first announced in 2007 by Accellera, many of the early features- like explicit supply port, supply net and the power state table (PST)- governed UPF based low power design verification methodologies mainly from post synthesis levels and onward. However, the recent update of IEEE 18013 specifies intrinsic flexibility to associate a power domain with a supply set and implicate infinite ordered list of power states, augmented with incrementally refinable arguments for the objects.

-

Abstract

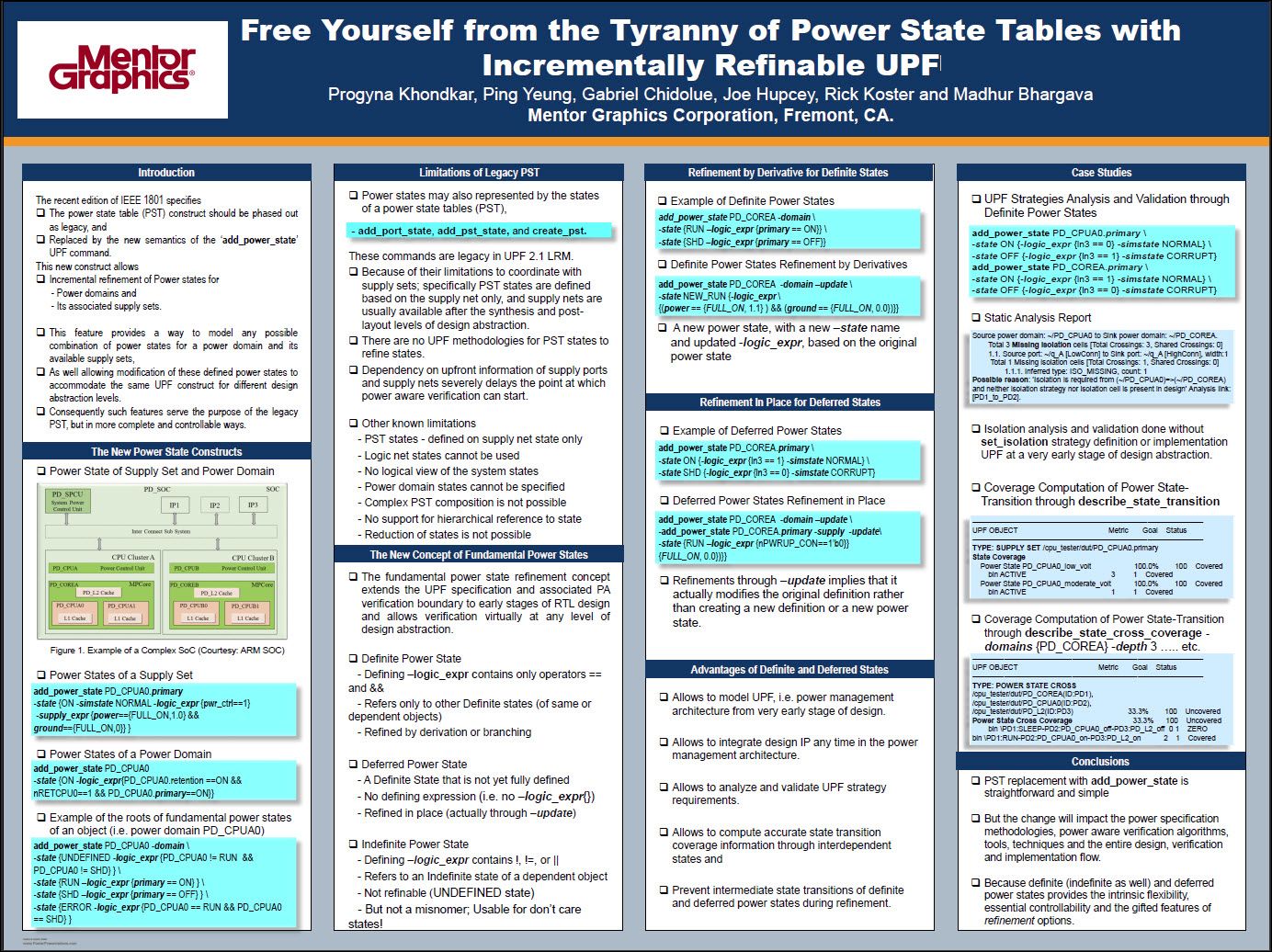

The recent edition of IEEE 1801 specifies the power state table (PST) construct should be phased out as legacy, and instead be replaced by the new semantics of the 'add_power_state' UPF command. This paper starts with investigating the limitations of legacy PST in a complex SoC design verification environment, and how to reap the benefits of the incrementally refinable power state features through the fundamental constructs of 'add_power_state'.

In order to comprehend the benefits of new semantics over PST, we perceived the new concepts of definite, indefinite and deferred power states at different design level of abstractions and connect them to demonstrate in power aware (PA) static and dynamic verification methodologies.

The conceptual sets of these fundamental power states provide a framework for verification engineers and tools to comprehend refinement of power states in a successive refinement flow as information about details of the design become incrementally available. In practice we extended this conceptual set as foundation of power aware static and dynamic verification techniques. Eventually the power state concept realization also allows us to probe further into the power management components for design and IP integration in different levels of design abstractions. Our approach shows validation procedures for UPF strategies through PA static verification. With design examples and case studies we also demonstrated how to achieve PA design verification closure with state and transition coverage, as well interdependent state's cross-coverage of power domains in more flexible and controllable ways.

Introduction

Since UPF was first announced in 2007 by Accellera, many of the early features- like explicit supply port, supply net and the power state table (PST)- governed UPF based low power design verification methodologies mainly from post synthesis levels and onward. However, the recent update of IEEE 18013 specifies intrinsic flexibility to associate a power domain with a supply set and implicate infinite ordered list of power states, augmented with incrementally refinable arguments for the objects. The objects are the rudimentary parts of the power supply architecture and the design elements, like supply sets, power domains, design groups, design models and design instances, collectively known as objects.2,3

The new power states definition completely replaces the conventional and tedious PST and enables multiple possible combinations of power states and their transitions models for the objects at any level of design abstraction. The incremental refinement features allow users to define new power states either on the original or on its derivatives entities for any object. Such power states provide more flexibility to represent different operational modes of a design with more controllability.

-

Download Paper

-

Free Yourself from the Tyranny of Power State Tables with Incrementally Refinable UPF

Low Power Mar 20, 2017 pdf

-