Search Results

Filters

Advanced Search

2262 Results

-

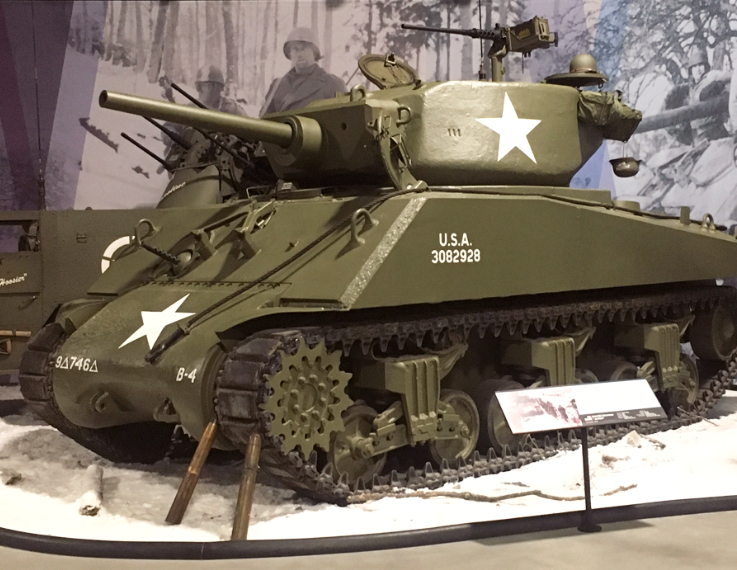

Verification Academy Live Hudson

Seminar - Jun 09, 2026 by Joe Hupcey

This seminar will provide design engineers and verification teams with the knowledge and tools needed to advance their workflows using the latest AI-driven automation, intelligent verification platforms, and industry-proven methodologies. Tuesday, June 9, 2026 | 9:00 AM - 5:00 PM EDT Location American Heritage Museum 568 Main St Hudson, MA 01749 +1 (978) 562-9182 This event is in-person only — there is no support for remote participation.

-

AI for Early SoC Security Verification

Webinar - Jun 03, 2026 by Beau Bakken

In this webinar, you will learn that Caspia Technologies has partnered with Siemens EDA to deliver the Questa CODAx solution, a security-aware static verification tool for early RTL security analysis.

-

Verification Academy Live BRNO University of Technology

Seminar - May 21, 2026 by Joe Hupcey

Verification Academy Live BRNO will explore the latest trends shaping modern functional verification and how new techniques are redefining productivity, scalability, and confidence in complex designs. Thursday, May 21, 2026 | 9:00 AM - 3:15 PM CEST Location BRNO University of Technology Bozetechova 1st Floor, A112 612 00 Brno Czech Republic +420 5 4114 1144

-

Breaking Bandwidth Barriers in the AI Era: Scaling PCIe with Retimers and Optical Innovation

Webinar - May 20, 2026 by Tufail Ansari

In this webinar, we will talk about PCIe Gen8 Retimer and Optical retimer, and its key applications, which includes use of optical retimer in GPU and AI accelerators. Further, we will explain the Four-Retimer Aware (FRA) feature and the rules that apply to loopback, lane margining and SKP ordered sets.

-

Join Me at DVClub Austin - May 20, 2026

Resource (Verification Horizons Blog) - May 11, 2026 by Harry Foster

The semiconductor industry is entering one of the biggest transitions I’ve seen in my career. The traditional boundaries that once separated hardware, software, physics, packaging, and system behavior are rapidly disappearing. Verification engineers are no longer validating isolated digital logic — we’re increasingly responsible for ensuring correctness across highly interconnected, multi-domain systems.

-

Enabling Formal Verification at Scale: An Agentic AI-driven Approach to RTL Bring-up

Conference - Apr 28, 2026 by Nirmala Balakrishnan

This session describes a verification methodology transformation that enabled a design team to adopt formal verification techniques despite being completely new to formal flows. The team previously relied heavily on simulation-based verification without static analysis or formal methods, with limited personnel and expertise to write properties or deploy formal tools effectively.

-

Broadcom: Reining in the Complexity of DFT Verification

Conference - Apr 28, 2026 by Michael Batek

As semiconductor complexity grows unabated, featuring hundreds of physical core instances and multi-die architectures, validating critical Design for Test (DFT) structures has become exceedingly difficult. The practical size of physical blocks isn't keeping pace with design size, leading to a proliferation of components requiring verification across design generations. This session will introduce techniques and methodologies developed to address these challenges.

-

Advancing Simulation Performance with Siemens QDX on MSFT Cobalt Silicon

Conference - Apr 28, 2026 by Sandesh Putturaya

With increasing semiconductor complexity, achieving robust DFT verification demands both high-quality simulation and scalable performance. Microsoft has partnered with Siemens to integrate Questa One Sim into our verification flows, enabling significant improvements in simulation efficiency and accuracy across timing and non-timing test modes. By deploying QDX, we’ve achieved dramatic runtime reductions, cutting verification cycles from two weeks to just a few days.

-

OnSemi: Unified Verification Platform (VPlatform)

Conference - Apr 28, 2026 by Yijun Loh

VPlatform is a comprehensive verification platform built on the UVMF, standardizing verification processes across OnSemi's teams and business units. It establishes a unified verification flow ensuring consistent architecture, best practices, and seamless collaboration. VPlatform enables easy VIP integration across diverse products, creating a scalable verification infrastructure.

-

Connected Verification and Validation: The Seamless Link Between Simulation and Emulation

Conference - Apr 28, 2026 by Harry Foster

As semiconductor complexity continues to escalate with AI/ML SoCs and advanced architectures, the industry faces a critical challenge: first silicon success rates are declining while project schedules slip further behind. Traditional verification approaches can no longer keep pace with the demands of modern chip design. This panel explores how connected verification and validation solutions create seamless workflows between simulation and emulation to tackle challenges more effectively.

-

From Apps to Orchestration: Agentic AI for Autonomous RTL Signoff with Questa One Agentic Toolkit

Webinar - Apr 22, 2026 by Ronen Shoham

In this webinar we will demonstrate how the Questa One Agentic Toolkit - announced in February 2026 and built on the industry-leading Questa One verification solution - transforms verification from isolated applications into intelligently orchestrated workflows through purpose-built Agentic AI that autonomously reasons, plans, and executes strategies while keeping engineers in the loop with approval controls at critical decision points.

-

From Apps to Orchestration: Agentic AI for Autonomous RTL Signoff with Questa One Agentic Toolkit

Resource (Slides (.PDF)) - Apr 22, 2026 by Ronen Shoham

Join us to explore how this open, MCP-based architecture enables seamless integration with GitHub Copilot, Claude Code, Cursor, Cline, or Siemens Fuse, supports vendor-neutral AI models (OpenAI, Anthropic, NVIDIA Nemotron), and delivers autonomous RTL signoff that liberates engineers from repetitive tasks while preserving human oversight for trusted design closure available for deployment today.

-

Why DFT Verification Signoff Is the Hidden Risk Threatening Your Next Tapeout

Resource (Verification Horizons Blog) - Apr 14, 2026 by Jake Wiltgen

Today’s chips integrate billions of transistors, dozens of IP blocks, and deeply hierarchical architectures, all of which must not only function correctly, but must also be testable after manufacturing. Design for Test (DFT) verification is a critical sign-off benchmark ensuring your test strategy and implementation is viable once chips start coming back.

-

BUGGED OUT Podcast - Episode 4: Vladislav Palfy

Resource (Podcast) - Apr 13, 2026 by Harry Foster

In episode 4, Harry Foster talks with Vladislav Palfy, Director of Solutions Management at Siemens EDA, about why coverage closure has become one of the biggest bottlenecks in modern verification. Drawing on insights from his white paper, Questa One Unified Coverage Solution: Transforming Verification Through Intelligence .

-

BUGGED OUT Podcast

Podcast - Apr 13, 2026 by Harry Foster

Every chip has bugs — the real question is how fast you can find and fix them. BUGGED OUT is the bite-sized podcast where we shine a light on the art (and science) of functional verification.

-

PCI Express 8.0: Powering AI, Cloud, and HPC with Transformative Interconnect Technology

Resource (Verification Horizons Blog) - Apr 09, 2026 by Gyanaranjan Khuntia - Siemens EDA

We are living through a data revolution that’s fundamentally changing how we design and build technology. From the neural networks that power tomorrow’s autonomous vehicles to the massive computational clusters that train the next generation AI models, one truth has become crystal clear: the bottleneck is not just about processing power anymore—it’s how fast we can move data between components.

-

DVCon US Keynote: Why Verification Must Evolve in the Convergence Era

Resource (Verification Horizons Blog) - Mar 25, 2026 by Harry Foster

At DVCon US 2026, a keynote delivered by three speakers—Abhi Kolpekwar (Siemens EDA), Jean-Marie Brunet (Siemens EDA), and Alon Shtepel (Micron)—shared a simple but important message: Verification is no longer a scaling problem. It’s a systems problem. For years, the industry has successfully handled increasing design size. More transistors? Add more compute. More IP? Run more regressions. That model served us well.

-

Verification Engineers Are Poised to Become Verification Scientists

Resource (Article) - Mar 19, 2026 by Max Maxfield - EE Journal

There are many ways to categorize engineers—to “slice and dice” them, if you will. I’m speaking figuratively, of course (we don’t want anyone to get any unfortunate ideas…especially since… the incident). Just sticking to the electronics realm, we have analog and digital, hardware and software, those who simulate and those who solder, those who document and those who don’t—and the French.

-

Shift-Left Compute Subsystem RTL Sign-Off with Software Aware VIP

Webinar - Mar 11, 2026 by Luis Rodriguez

In this webinar we present a scalable methodology to accelerate the development and verification of Compute Subsystems such as Arm® Neoverse™ V3 Compute Subsystem (CSS)-based designs, with a shift-left in simulation and signoff using Avery Protocol VIP, CSS VIP, Software Aware VIP, Arm Fast Models and QEMU models.

-

Shift-Left Compute Subsystem RTL Sign-Off with Software Aware VIP

Resource (Slides (.PDF)) - Mar 11, 2026 by Luis Rodriguez

Design and verification teams consistently tell us that compute subsystems require software bring up much earlier than ever before. They need UEFI and Linux to run in simulation, they need protocol accuracy from day one, and they need a predictable path to signoff while integration risks rise every quarter. This struggle has become a shared industry reality.

-

Agentic AI for RTL Signoff: Gen AI for Chip Design Flows using Questa Toolkit

Conference - Mar 05, 2026 by Ronen Shoham

This tutorial will detail the architectural principles behind an Agentic AI approach, demonstrating how MCP facilitates interoperability and enables autonomous, trusted RTL signoff. Attendees will gain insights into fostering design quality and liberating engineers from repetitive tasks.

-

Beyond Bigger Designs: Rethinking Verification for the Era of Convergence

Conference - Mar 03, 2026 by Abhi Kolpekwar

In this keynote from DVCon U.S. 2026, experts from Siemens EDA and Micron Technology explore how verification must evolve to address this new era of system complexity. Traditional, phase-based verification approaches are giving way to continuous, feedback-driven processes that span the entire product lifecycle.

-

Siemens accelerates integrated circuit design and verification with agentic AI in Questa One

Resource (Press Release) - Feb 27, 2026 by Siemens PR

Siemens today announced the Questa One Agentic Toolkit, which brings domain-scoped agentic AI workflows to its Questa™ One smart verification software portfolio to accelerate creation, verification planning, execution, debugging and closure to achieve trusted RTL sign-off faster while transforming how engineers approach integrated circuit (IC) design and verification tasks.

-

Human-Centered Agentic AI Workflows for RTL Verification

Paper - Feb 27, 2026 by Harry Foster

The Questa One Agentic Toolkit extends the Questa One solution with human-centered agentic workflows that embed intelligence directly into these workflows, rather than isolated tools. By combining engine-native context, goal-driven agents, deliberate human-in-the-loop design, and open integration, the Questa One Agentic Toolkit provides a pragmatic path toward more adaptive and scalable productivity, supporting faster progress without sacrificing trust or rigor.

-

Human-Centered Agentic AI Workflows for RTL Verification

Resource (Paper (.PDF)) - Feb 27, 2026 by Harry Foster

In this paper, you will learn that productivity challenges in modern semiconductor development stem less from individual tool limitations and more from process-level complexity across design creation, verification, and iteration. Agentic EDA addresses this shift by embedding intelligence directly into workflows that span creation and validation.