Intent Meets Implementation: Verifying Complex Power Strategies with UPF 4.0

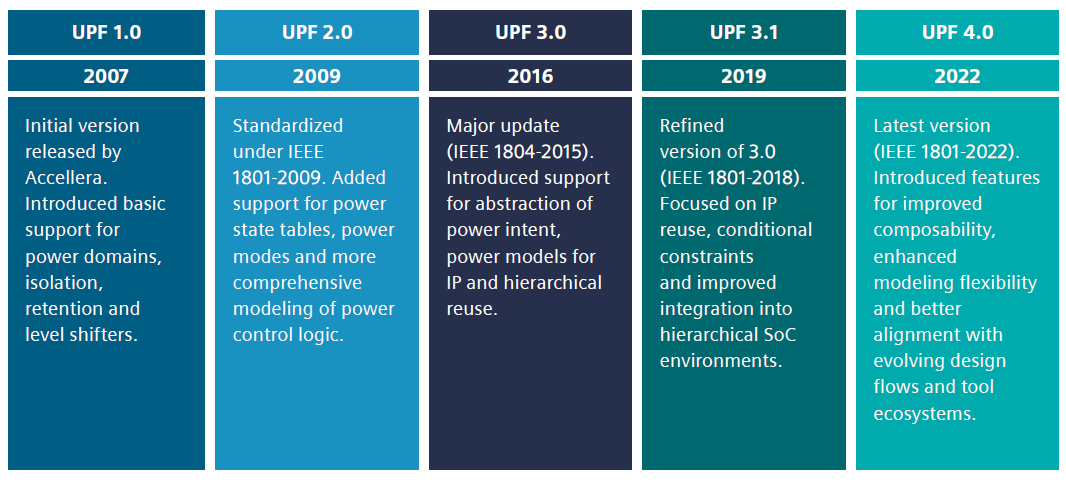

Questa One Sim PowerAware supports several of the most commonly used features available in UPF 4.0. This white paper takes a deep dive into UPF 4.0. What’s new, why it matters and how it fits into the evolving landscape of SoC design. We’ll start with a look at how UPF has grown over the years and why version 4.0 is a significant step forward for teams building large, power-aware systems. We'll also walk through practical tips and real-world challenges that teams face when rolling out UPF 4.0.

-

Introduction

Power efficiency has become a must-have in today’s ASIC and SoC designs. It’s no longer just about squeezing out more performance. It’s about doing so without draining the battery, wasting energy or overheating the system. Whether the chip is headed for a smartphone, a server rack in an AI datacenter or the control system of an autonomous vehicle, managing power wisely is as critical as meeting timing or ensuring functional correctness.

The challenge, of course, is that modern SoCs aren’t getting any simpler. They’re packed with multiple CPUs, accelerators, memory hierarchies and high-speed interfaces, all operating under different performance and power constraints. To keep energy use in check, engineers rely on techniques like power gating, voltage islands and dynamic voltage and frequency scaling (DVFS). But these strategies don’t work in isolation. They depend on careful coordination between RTL, verification and implementation teams.

And here’s where things get tricky. Without a consistent way to describe and validate power intent across the entire design flow, teams risk running into serious problems: logic that breaks when a domain powers down, blocks that consume more energy than expected, or silicon that behaves unpredictably in the lab. Any one of these can mean missed deadlines, late-stage bugs or expensive respins. That’s why getting power intent right from the start of the design process is more important than ever.

Questa One Sim PowerAware supports several of the most commonly used features available in UPF 4.0. These features are tested and being actively used in the customer community to verify the power intent of their designs.

The Role of UPF in Power Aware SoC Design

As SoCs have become more power-sensitive and more complex, design teams need a better way to describe and manage power intent. That’s where the Unified Power Format (UPF) comes in. Originally developed to bring some structure and consistency to how power intent is specified and verified, UPF has grown into a key part of the low-power design toolkit. It allows teams to express power strategies in a way that’s independent of RTL logic, but still tightly connected to how the design behaves.

Today, power intent isn’t just a set-it-and-forget-it spec. It has to account for dynamic workloads, performance scaling and on-the-fly decisions made by the system’s power manager. UPF helps with that by providing a common language for defining domains, retention requirements, isolation rules and voltage conditions – and just as importantly, a way to simulate and verify them.

Using UPF, engineers can model how power states change over time and make sure those changes won’t break functionality. Whether it’s checking that clock gating doesn’t disable a critical path or making sure that a retained register wakes up with the right state, UPF helps teams catch problems early – before they show up on silicon.

Figure 1. The evolution of UPF.

-

Download Paper

-

Intent Meets Implementation: Verifying Complex Power Strategies with UPF 4.0

Low Power May 13, 2025 pdf

-