UVM Sans UVM: An Approach to Automating UVM Testbench Writing

The SystemVerilog1 UVM2 promises to improve verification productivity while enabling teams to share tests and testbenches between projects and divisions. This promise can be achieved; the UVM is a powerful methodology for using constrained randomization to reach higher functional coverage goals and to explore combinations of tests without having to write each one individually. Unfortunately, the UVM promise can be hard to reach without training, practice and some significant expertise.

-

Introduction

There are many organizations that offer “UVM training”, “Simple UVM”, “Easy UVM”, and “Easier UVM”. A google search will reveal many places to find easy UVM and get help. Those proponents of easy UVM supply training, support, and the actual doing of the work. But there is a cost in time and money. A google search will also reveal many places that supply code generators – “UVM templates”, “UVM generator”. There are also frameworks layered on top of the UVM library – for example, “UVM Framework”.

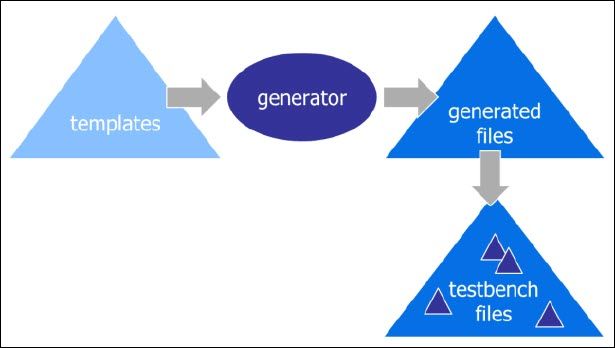

Our belief is that a framework or code generated template system is the right solution to get started with the UVM. The frameworks, code generators and templates leverage the UVM experience of previous verification efforts. Additionally, success with the generated code doesn’t require knowing all the details at the start. Over time the framework, generator and template can grow as the UVM verification experience on the team grows.

This paper is targeted towards a verification team without any UVM background and it describes a simple template and generator, without any extra time overhead, and without any extra budget overhead. This paper offers a simple solution to taking that first step. The generator and templates do require SystemVerilog knowledge, and a general understanding of what a UVM verification environment looks like.

There will be typing – but it is limited to a few well-defined sections of code that are design specific – very well known to the verification and design teams building a UVM testbench. With a few simple edits the generated code can be used on the same day. Our experience deploying the templates at customers is that within 3 to 8 hours, a new UVM based testbench is up and running.

Figure 1: Idealized generator

The templates are not automatic – in the sense that you still have to do some work. You must describe your transaction. You must describe your bus. You must design the driver of the bus and the monitor of the bus. You may need to write a “golden model”. You have to design how the testing will occur – for example, how to test multiple interfaces. All of the work that you must do occurs within the generated boilerplate. You must be able to write SystemVerilog code, but you don’t need to know the details of the UVM.

-

Download Paper