Boost Verification Results by Bridging the Hardware/Software Testbench Gap

Today's complex designs increasingly include at least one, and often more, embedded processors. Given software's increasing role in the overall design functionality, it has become increasingly important to leverage the embedded processors in verifying hardware/software interactions during system-level verification. This paper presents a UVM-based package for software-driven verification and presents applications of this package that enable more-comprehensive system-level verification.

-

Introduction

Complexity begets complexity. Which is to say, to run properly and fully realize their intended behavior, today's intricate hardware designs with tens of millions (or more) gates inevitably require ever more nuanced and elaborate software. This tight coupling means that the traditional verification process, where both hardware and software are designed and verified in isolation and then integrated late in the design cycle, is less and less workable. What is needed is a two-way street for verifying low-level software and verifying the hardware used by the embedded software and doing both as early in the process as possible.

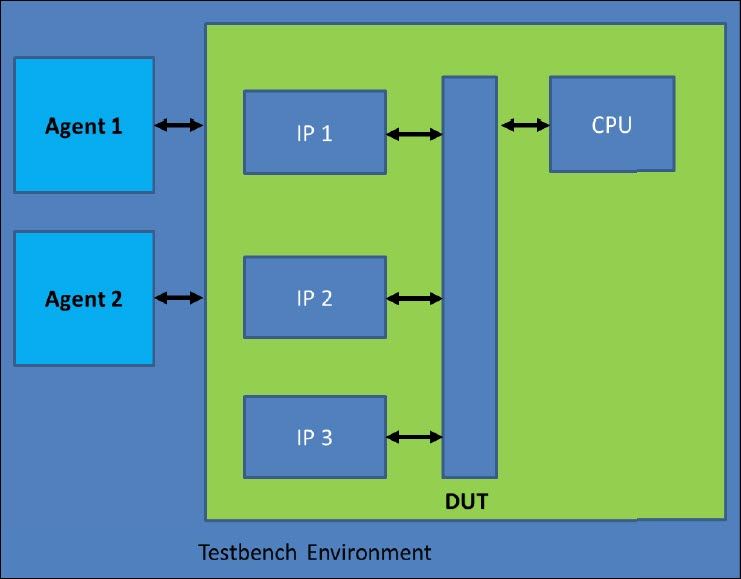

A software-driven verification environment differs in some fundamental ways from a hardware-centric verification environment. Figure 1 shows a typical hardware-centric SoC verification environment. Agents within the testbench environment apply stimulus to the design via its interfaces. Software runs on the processor within the design to manage the component IP blocks. From a structural perspective, the processor, and the software running on it, is part of the design.

In the diagram below, the hardware and software portions of the testbench environment run in isolation, which leads to several problems. First, the isolation makes it very difficult or impossible to coordinate the operation of software running on the processor with stimulus provided from the hardware-centric

testbench environment. It is also extremely challenging to achieve the level of comprehensive verification needed to ensure proper design operation, since the software-driven stimulus is unable to take advantage of advanced stimulus generation techniques or to contribute to functional coverage metrics.

Figure 1: Hardware-Centric Verification Environment

The comprehensiveness of verification can be increased by making the software running on the processor part of the verification environment. For example, in the case of this design, IP 3 has no external interfaces. Its operation in conjunction with IP 2 can really only be verified by controlling IP 3 via software, while applying stimulus to the external interface of IP 2. Enabling this coordination and cooperation of the hardware-centric and embedded-software portions of the testbench is a key goal of a software-driven verification environment.

-

Download Paper