In reply to tirumalrao_m:

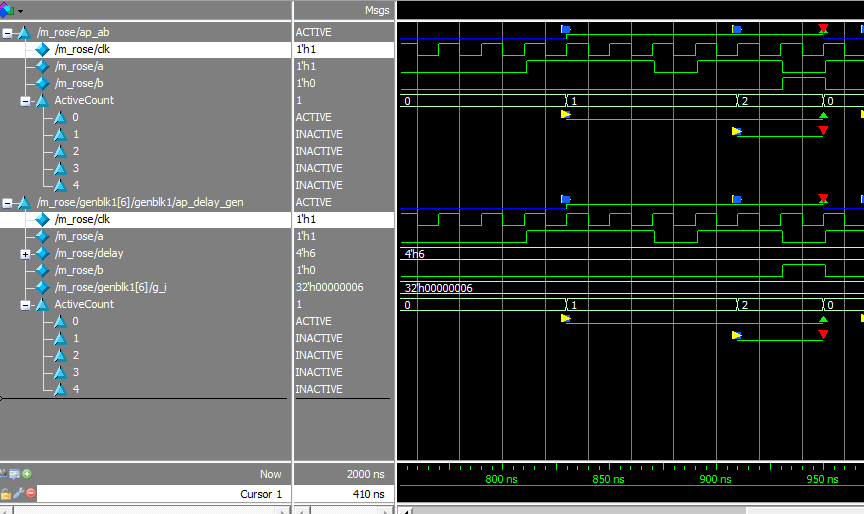

I want to check b rose 6 cycle after a raises, and during 6 cycle b should be zero, should not toggle.

Two solutions:

- fixed 6 cycles for rose(b)

- Delay-based on a variable

module m_rose;

bit clk, a, b;

bit[3:0] delay=6;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

// I want to check b rose 6 cycle after a raises,

// and during 6 cycle b should be zero, should not toggle.

ap_ab: assert property(

$rose(a) |=> !b[*5] ##1 $rose(b));

generate for (genvar g_i=0; g_i<16; g_i++) begin

if(g_i ==0)

ap_delay_gen: assert property ($rose(a) && g_i==delay

|=> !b[*g_i] ##1 $rose(b)); // same as |=> $rose(b)

else

ap_delay_gen: assert property ($rose(a) && g_i==delay

|=> !b[*g_i-1'b1] ##1 $rose(b));

end endgenerate

http://systemverilog.us/m_rose.sv with simple testbench

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SystemVerilog Assertions Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115