In reply to tirumalrao_m:

In reply to ben@SystemVerilog.us:

I tried above thing but for me g_i is not fixed It will changes during run.

It depends on some other variable in the simulation and that variable changes based on setting.

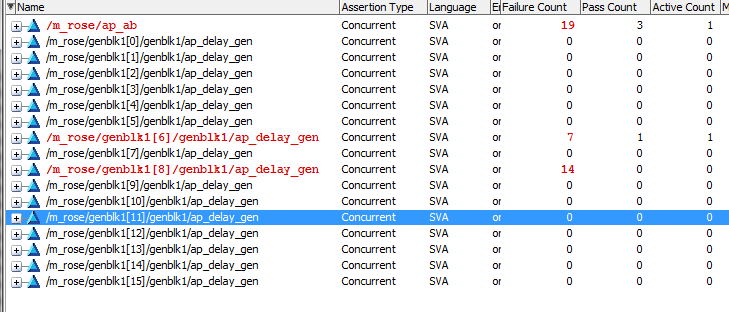

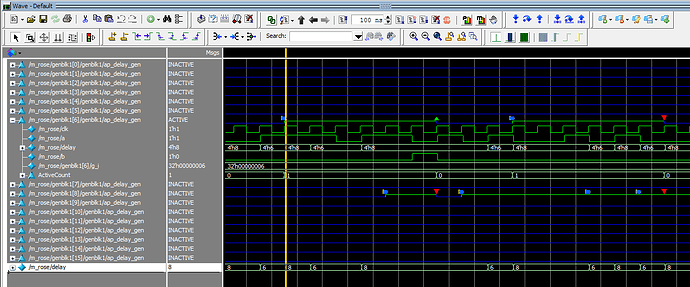

You missed my main point on the generate. The following code generates 16 separate assertions: Thus, the variable can change value. Note that in eh antecedent I have

$rose(a) && g_i==delay, thus, if among those 16 assertions, the ones that don’t match the delay create vacuous assertions. The only one that matches and has a successful $rose fire.

generate for (genvar g_i=0; g_i<16; g_i++) begin

if(g_i ==0)

ap_delay_gen: assert property ($rose(a) && g_i==delay

|=> !b[*g_i] ##1 $rose(b)); // same as |=> $rose(b)

else

ap_delay_gen: assert property ($rose(a) && g_i==delay

|=> !b[*g_i-1'b1] ##1 $rose(b));

end

endgenerate

Specifically, you would get

genblock(0)ap_delay_gen: assert property ($rose(a) && 0==delay

|=> !b[*0] ##1 $rose(b)); // same as |=> $rose(b)

genblock(1)ap_delay_gen: assert property ($rose(a) && 1==delay

|=> !b[*1-1'b1] ##1 $rose(b));

...

genblock(15)ap_delay_gen: assert property ($rose(a) && 15==delay

|=> !b[*15-1'b1] ##1 $rose(b));

Here is the code and simulation results.

It looks like I could have done this instead, I don’t need the 0 case in this case. :

generate for (genvar g_i=1; g_i<16; g_i++) begin

ap_delay_gen: assert property ($rose(a) && g_i==delay

|=> !b[*g_i-1'b1] ##1 $rose(b));

end

endgenerate

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SystemVerilog Assertions Handbook 4th Edition, 2016 ISBN 978-1518681448