Q. Write Code for Pattern Detector 10110. Input to DUT is 1 bit and output is 1 bit.

How can I implement without queue?

If I change queue to array in below code I get flag=1 twice. Why?

EDA Link: EDA Playground

Design.sv

module pattern_detect(input clk, input rst, input bit in, output flag);

logic pat_seq[\$]='{1,0,1,1,0};

logic pat_in[\$]='{0,0,0,0,0};

reg flag=0;

always @(posedge clk) begin

if(!rst) begin

pat_in.pop_front();

pat_in.push_back(in);

//Issue with using array

// pat_in[4]<=pat_in[3];

// pat_in[3]<=pat_in[2];

// pat_in[2]<=pat_in[1];

// pat_in[1]<=pat_in[0];

// pat_in[0]<=in;

if(pat_in == pat_seq) begin

flag <= 1;

$display(" *************************** ");

$display("flag is 1 @time=%0d", $time);

$display(" *************************** ");

foreach(pat_in[i]) begin

$display("pat_in[%0d]=%0d", i, pat_in[i]);

end

$display("***************************");

end

else begin

flag <= 0;

$display("flag is 0 @time=%0d", $time);

foreach(pat_in[i]) begin

$display("pat_in[%0d]=%0d", i, pat_in[i]);

end

end

end

if(rst)

flag <=0 ;

end

endmodule

**[u]Testbench.sv[/u]**

module test;

reg clk=0;

reg rst=1;

reg in=0;

wire flag;

pattern_detect pat(.clk(clk), .rst(rst), .in(in), .flag(flag));

initial begin

forever begin

#10 clk = ~clk;

end

end

initial begin

// Dump waves

$dumpfile("dump.vcd");

$dumpvars(1, test);

#10 rst=0;

in=0;

#20 in=1;

#20 in=1;

#20 in=0;

#20 in=1;

#20 in=1;

#20 in=0;

#20 in=1;

#20 in=0;

#20 in=0;

#20 in=1;

#20 in=0;

#20 in=1;

$finish;

end

endmodule

Log

flag is 0 @time=10

pat_in[0]=0

pat_in[1]=0

pat_in[2]=0

pat_in[3]=0

pat_in[4]=0

flag is 0 @time=30

pat_in[0]=0

pat_in[1]=0

pat_in[2]=0

pat_in[3]=0

pat_in[4]=1

flag is 0 @time=50

pat_in[0]=0

pat_in[1]=0

pat_in[2]=0

pat_in[3]=1

pat_in[4]=1

flag is 0 @time=70

pat_in[0]=0

pat_in[1]=0

pat_in[2]=1

pat_in[3]=1

pat_in[4]=0

flag is 0 @time=90

pat_in[0]=0

pat_in[1]=1

pat_in[2]=1

pat_in[3]=0

pat_in[4]=1

flag is 0 @time=110

pat_in[0]=1

pat_in[1]=1

pat_in[2]=0

pat_in[3]=1

pat_in[4]=1

flag is 1 @time=130

pat_in[0]=1

pat_in[1]=0

pat_in[2]=1

pat_in[3]=1

pat_in[4]=0

flag is 0 @time=150

pat_in[0]=0

pat_in[1]=1

pat_in[2]=1

pat_in[3]=0

pat_in[4]=1

flag is 0 @time=170

pat_in[0]=1

pat_in[1]=1

pat_in[2]=0

pat_in[3]=1

pat_in[4]=0

flag is 0 @time=190

pat_in[0]=1

pat_in[1]=0

pat_in[2]=1

pat_in[3]=0

pat_in[4]=0

flag is 0 @time=210

pat_in[0]=0

pat_in[1]=1

pat_in[2]=0

pat_in[3]=0

pat_in[4]=1

flag is 0 @time=230

pat_in[0]=1

pat_in[1]=0

pat_in[2]=0

pat_in[3]=1

pat_in[4]=0

$finish called from file “testbench.sv”, line 50.

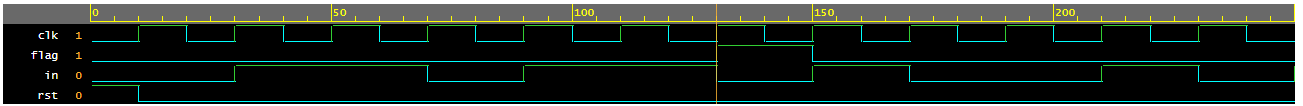

Waveform