In reply to warnerrs:

Below is a link to a simple model that demonstrates that a wire (data) in an interface can be drivern by a task in a class.

http://SystemVerilog.us/fv/ifc_driver.sv

Key elements from above link

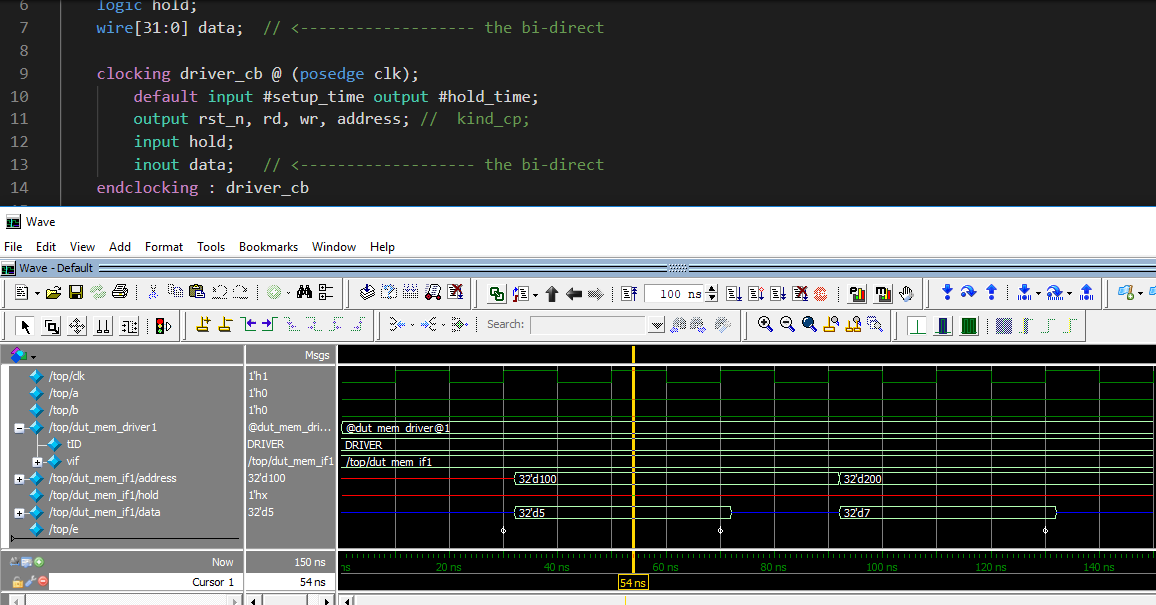

interface dut_mem_if (input logic clk);

...

wire[31:0] data; // <------------------- the bi-direct

clocking driver_cb @ (posedge clk);

default input #setup_time output #hold_time;

output rst_n, rd, wr, address; // kind_cp;

input hold;

inout data; // <------------------- the bi-direct

endclocking : driver_cb

endinterface : dut_mem_if

class dut_mem_driver;

string tID="DRIVER";

virtual interface dut_mem_if.drvr_if_mp vif;

// ...

virtual task write_task(logic [31:0] data, address);

vif.driver_cb.rst_n <= 1'b1;

...

this.vif.driver_cb.data <= data;

this.vif.driver_cb.address <= address;

repeat(3) @ (this.vif.driver_cb);

this.vif.driver_cb.wr <= 1'b0;

this.vif.driver_cb.rd <= 1'b0;

this.vif.driver_cb.data <= 'Z;

endtask : write_task

endclass : dut_mem_driver

module top;

event e; // for debug

bit clk, a, b;

dut_mem_driver dut_mem_driver1;

dut_mem_if dut_mem_if1(clk);

initial forever #10 clk=!clk;

initial begin

dut_mem_driver1 = new();

dut_mem_driver1.vif= dut_mem_if1;

#30 -> e;

@(posedge clk);

dut_mem_driver1.write_task(5,100);

-> e;

@(posedge clk);

dut_mem_driver1.write_task(7,200);

->e ;

@(posedge clk);

$stop;

end

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment