Hi,

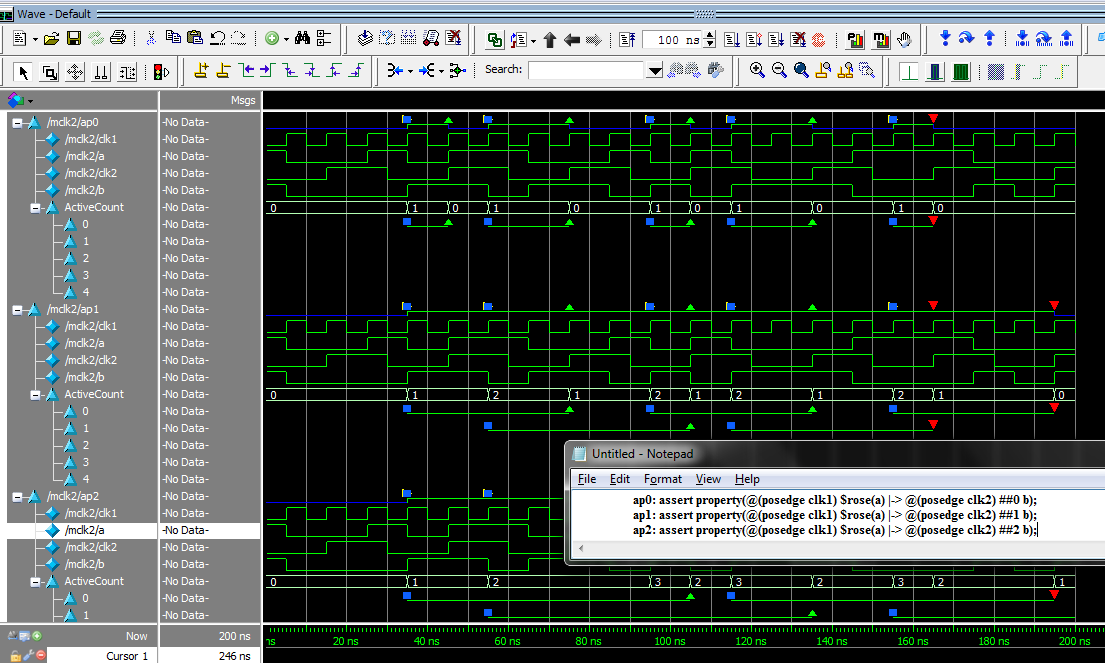

Background: I am trying to verify my fully asynchronous FIFO using SVA. The read clock domain can indicate that the FIFO is empty and the write clock domain can indicate that the FIFO is full. My design allows the circuit to indicate that it is both empty and full for the time that it takes to synchronize a signal from one domain to another, this takes two (receiving domain) clock cycles. Thus the FIFO can indicate that it is both full and empty from posedge ckA to two posedge ckB later. My trouble is in allowing this using SVA. The code I am using now is:

property pr_ifAnotBstable(a, b, ckA, ckB);

disable iff(arstWrite | arstRead)

@(posedge ckA) $rose(a) |->

@(posedge ckB) ##1 !b;

endproperty

This causes the assertion to sample rose on ckA, then wait one ckA, then wait two ckB before asserting the statement. What i want is: sample rose on ckA, then wait two ckB before asserting the statement. How can I do this?

Side note: I have tried with |=> and |-> ##1 (clock handovers), but this changes nothing. From Doulos’ documentation[1] it seems to me that I am doing this correctly, but that Questasim has a different definition of how this should be handled. When I try using |-> ##3 (which is supposed to be an illegal assignment) it diligently waits three ckA. This is according to [1] wrong, but this is not really a problem.

I am using Questasim 10.2b.

[1] Figure 7, Asynchronous Behaviors Meet Their Match with SystemVerilog Assertions, Doug Smith, Doulos