In reply to henrsol:

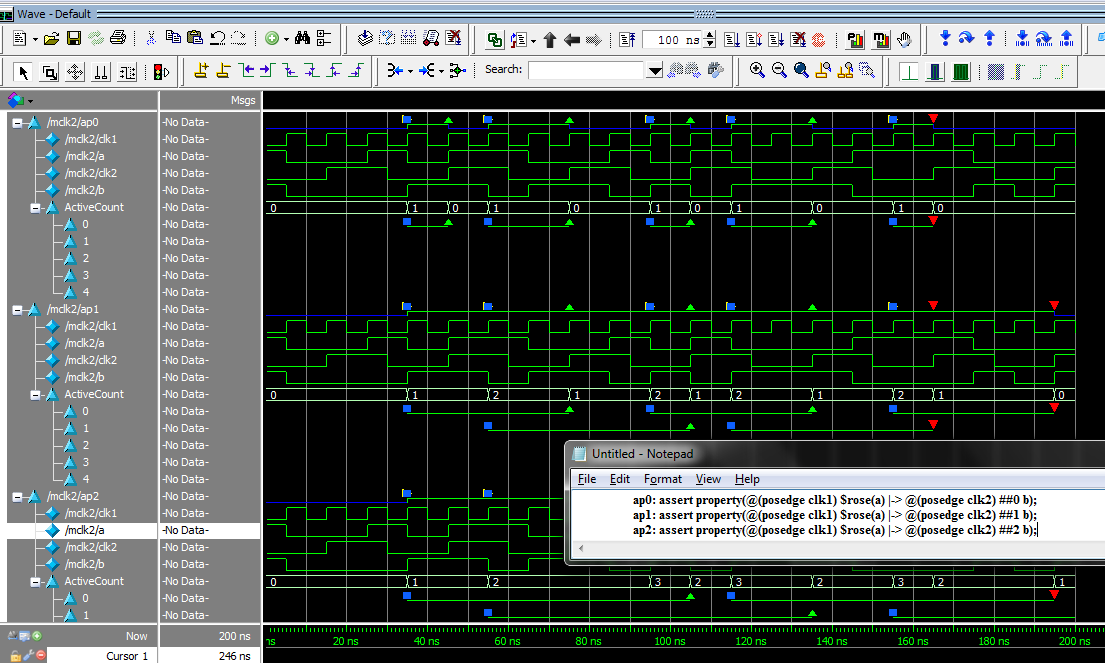

My apologies, I made a mistake. 1800’2012, 16.13.1 Multiclocked sequences explains the process, which is confusing, I agree.

The single delay indicated by ##1

is understood to be from the end point of the first sequence, which occurs at a tick of the first clock, to the nearest strictly subsequent tick of the second clock, where the second sequence begins

That means, in your case, for

@(posedge ckA) $rose(a) |->

@(posedge ckB) ##1 !b;

after the @(posedge ckA) $rose(a), you wait till the nearest (posedge ckB), and then after ##1 of (posedge ckB) signal b must be ==0.

If clk0 and clk1 are not identical, then the clocking event for the sequence changes after ##1. If clk0 and clk1 are identical, then the clocking event does not change after ##1, and the above sequence is equivalent to the singly clocked sequence @(posedge clk0) sig0 ##1 sig1

In that case after the @(posedge ckA) $rose(a), since the nearest (posedge ckB) is 0( there is no wait), and then after ##1 of (posedge ckB) signal b must be ==0.

The zero delay

indicated by ##0 is understood to be from the end point of the first sequence, which occurs at a tick of the first clock, to the nearest possibly overlapping tick of the second clock, where the second sequence begins.

That means, in your case, for

@(posedge ckA) $rose(a) |->

@(posedge ckB) ##0 !b;

after the @(posedge ckA) $rose(a), you wait till the nearest (posedge ckB), and then signal b must be ==0. If the clocks are identical (at that edge), then after the @(posedge ckA) $rose(a), NO wait, signal b must be ==0. Below are models I created.

http://SystemVerilog.us/mclk2.sv

http://SystemVerilog.us/mclk3.png

http://SystemVerilog.us/mclk3.sv

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SystemVerilog Assertions Handbook 3rd Edition, 2013 ISBN 878-0-9705394-3-6

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115