Hi,

I am writing and reading from the register by using (write and read) methods in UVM Reg Model.

Write and read is happening perfectly. And I am printing the values in Adapter.

But when I am reading the register bus2reg is called twice and my read data is getting override by 0 second time.

So when I am comparing with the Mirrored Value getting Comparison Fail.

Please give your Suggestions.

Thanks,

Raja Sekhar.

In reply to raja.kuraku:

Could you please provide some code regarding our environment, the test and the sequence you are starting for your test.

In reply to chr_sue:

Please find the attached Snippets

ENV Class:

Declaration : uvm_reg_predictor #(apb_seq_item) nvme_reg_predictor;

if (m_env_cfg.m_apb_agent_cfg.active == UVM_ACTIVE) begin

reg2apb = apb_reg_adapter::type_id::create ("reg2apb");

if (m_env_cfg.m_apb_rm.get_parent() == null) begin

m_env_cfg.m_apb_rm.apb_reg_top_block_map.set_sequencer (m_apb_agent.m_sequencer, reg2apb);

end

my_reg_predictor.map = m_env_cfg.m_apb_rm.apb_reg_top_block_map;

my_reg_predictor.adapter = reg2apb;

m_env_cfg.m_apb_rm.apb_reg_top_block_map.set_auto_predict(0);

m_apb_agent.m_monitor.apb_ap.connect(my_reg_predictor.bus_in);

end

TEST Class:

phase.raise_objection (this, "REG_Test started");

begin

apb_reg_wr_rd_seq_h = apb_reg_wr_rd_seq::type_id::create("apb_reg_wr_rd_seq_h");

apb_reg_wr_rd_seq_h.start (null);

#100ns;

end

phase.drop_objection (this, "REG_Test finished");

Sequence Class:

Declaration :

apb_reg_top_block model;

nvme_env_config m_env_cfg;

uvm_reg_data_t read_data;

uvm_reg_data_t rd_data;

_Task Body:_

write_reg(model.CAP_LOW,status,32'hFFFF_FFFF);

read_reg(model.CAP_LOW,status,read_data);

if(status == UVM_NOT_OK)

`uvm_error("REG_SEQUENCE","Status Is NOT OK During Read Operation")

rd_data = model.CAP_LOW.get_mirrored_value();

if(rd_data != read_data) begin

`uvm_error("APB_REG_SEQUENCE","^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^")

`uvm_error("APB_REG_SEQUENCE","^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^")

`uvm_error("APB_REG_SEQUENCE"," The Compared Value of Mirrored and Register Read is Wrong ")

`uvm_error("APB_REG_SEQUENCE","^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^")

`uvm_error("APB_REG_SEQUENCE","^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^")

end

In reply to raja.kuraku:

What is the access policy of that register? If it is WO reading back is OK.

If status is not OK, you are reading twice. See the code below:

read_reg(model.CAP_LOW,status,read_data);

if(status == UVM_NOT_OK)

`uvm_error("REG_SEQUENCE","Status Is NOT OK During Read Operation")

rd_data = model.CAP_LOW.get_mirrored_value();

In reply to chr_sue:

Thanks chr_sue for your response

Yes Its “RW” register.

And both the times the status is UVM_IS_OK.

There is no UVM_ERROR in my simulation.

In reply to raja.kuraku:

I was just reading again your first entry. What does it mean read and write works perfectly.

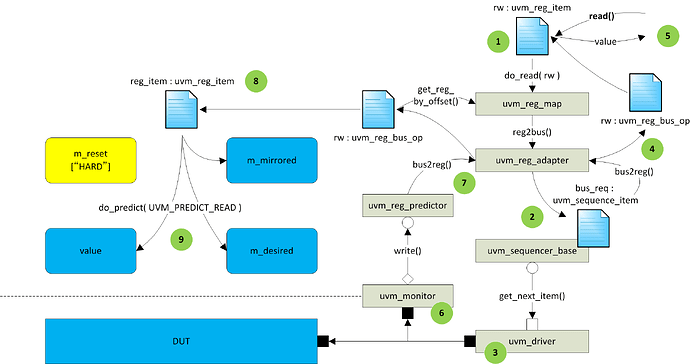

bus2reg is not a register. It is a method. Maybe you have to look here for some more details.

As per above code you have connected monitor to predictor,

possible call for bus2reg

- wait for end event from req or if provide response is 1 then wait for driven to put response.

bus_req.end_event.wait_on();

if (adapter.provides_responses) begin

uvm_sequence_item bus_rsp;

uvm_access_e op;

// TODO: need to test for right trans type, if not put back in q

rw.parent.get_base_response(bus_rsp);

adapter.bus2reg(bus_rsp,rw_access);

end

else begin

adapter.bus2reg(bus_req,rw_access);

end

- When monitor see that register read, it also call bus2reg,

so you will see bus2reg get called twice if you have monitor connected to predictor.as you are using same adapter.

I suspect your read response transaction from monitor is not correct as you mentioned it is getting overriden by 0 2nd time.

Image from ClueLogic Post will give you clear picture :

In reply to Vinay Jain:

I’m not sure if this clarifies the problem raka has, because I’m nor sure if raka deals with responses. To state one thing: you do not need the call get_response. A read gives back the value by calling bus2reg, and a write calls reg2bus.

raka our adapter code would be of interest.

In reply to chr_sue:

My first entry “Reads works Perfectly” mean to say that.

I am doing a register read operation and capturing the read_xtn in Monitor and writing to analysis port using write method. So whenever Monitor writes in to Analysis port bus2reg function will be called. In my condition bus2reg function is called by twice(Printing in Adapter). During first call read_data printing the read value and the second time printing ‘0’(Both times status is “UVM_IS_OK”).

I tried to control using one variable setting in monitor and checking in adapter bus2reg function, Still during read the read data {.value(read_data)} is getting override.

In reply to raja.kuraku:

Hai i am also facing same issue u got any soulution for this.if u got expalin plz.

Hi,

I think the bus2reg function is called twice because there are 2 components which call it: adapter and predictor. The second call doesn’t ‘override’ the value, just because the predictor (monitor of agent) some how can’t get the data. Could you check the connection between the predictor and the analysis port of monitor?

Regards,

Bach