In reply to No:

There are sayings that are good advice, particularly in software:

- KISS

- Why make it complicated when you can make it simple?

- Why make it simple when you can make it complicated?

SVA is rich, maybe too rich, in features and possibilities.

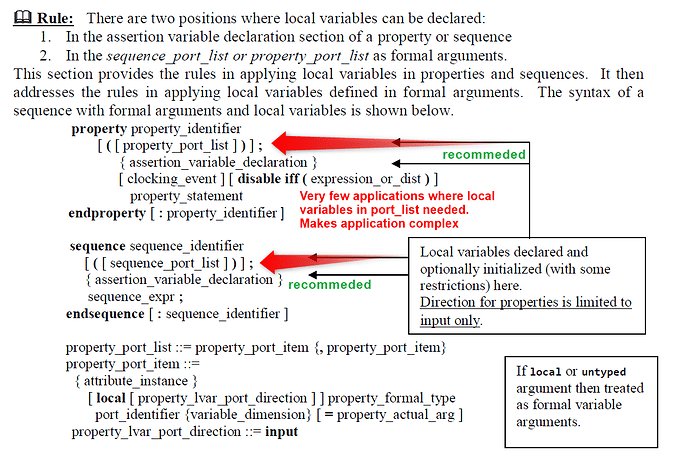

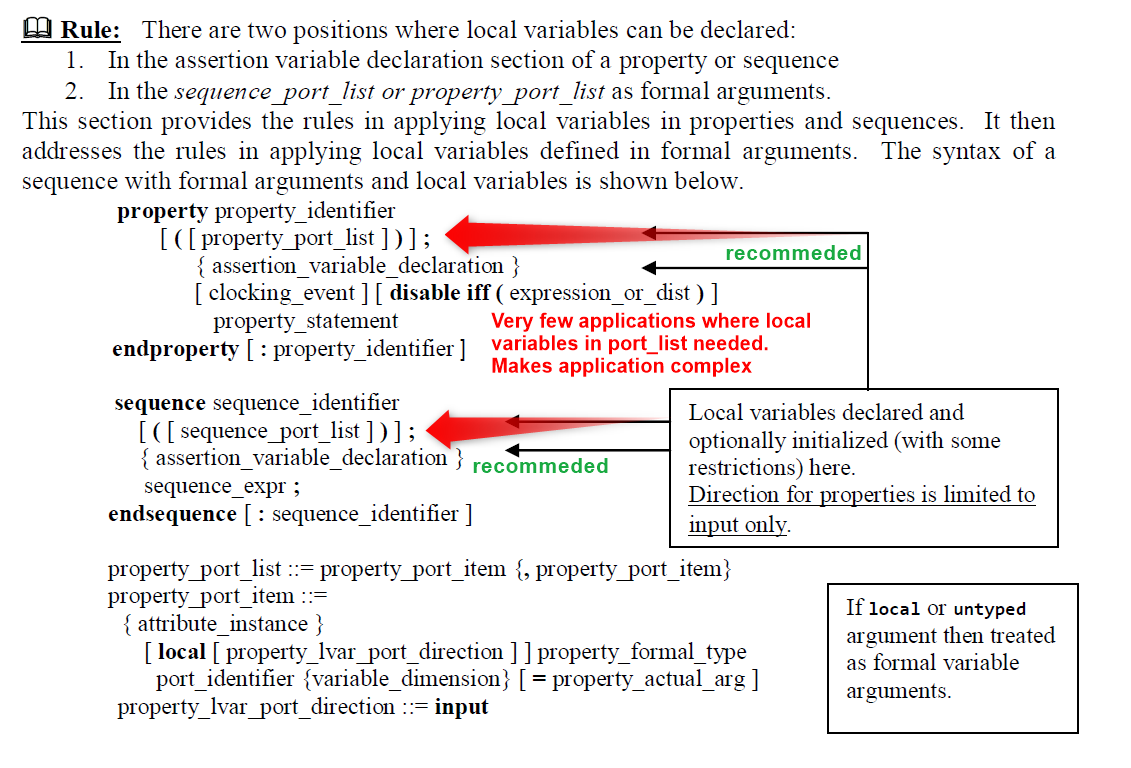

Declaring local variables in sequence_port_list is confusing. I wrote several books,

lots of SVA code, analyzed several users’s requirements and have never found the need to do that. Declare the local variables in the assertion_variable_declaration; it make it so much easier.

Here is an awful example that demonstrates why one may want to declare local variables in the port list. I say awful because it creates code that is hard to read an understand, and then you have to worry that you don’t violate the many rules of doing this local variable declaration in the port list. My advice, KISS!

bit clk, a, b, c;

default clocking cb_clk @ (posedge clk); endclocking

sequence q_local_formal_arguments2( local input int i=0, untyped j, k,

local output bit t);

(i>10, j=i) ##1 (1, j=data, t=1'b1) ##1 k;

endsequence

property p_test_untype;

int x, z; // local variable

bit r; // local variable

(a, x=10) ##1

q_local_formal_arguments2( .i(x), .j(z), .k(a), .t(r)) ##1 x==z ##0 r;

endproperty : p_test_untype

ap_test_untype: assert property(p_test_untype);

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) https://rb.gy/cwy7nb - Papers:

- Understanding the SVA Engine,

Verification Horizons - Reflections on Users’ Experiences with SVA

Reflections on Users’ Experiences with SVA - SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment

Udemy courses by Srinivasan Venkataramanan (http://cvcblr.com/home.html)

https://www.udemy.com/course/sva-basic/

https://www.udemy.com/course/sv-pre-uvm/