In reply to ben@SystemVerilog.us:

Ben as you pointed that the difference between the two is visible when it’s used as antecedent .

Hence I tried the following ::

property req_ack ;

`ifdef GO_TO

@( posedge clk ) $rose( req ) [ ->1 ] |=> $rose( ack ) ; // [E1]

`else

@( posedge clk ) $rose( req ) [ = 1 ] |=> $rose( ack ) ; // [E2]

`endif

endproperty

c_property : cover property ( req_ack ) $display(" TIME : %0t PASS " , $time ) ;

a_property : assert property ( req_ack ) else $display(" TIME : %0t FAIL " , $time ) ;

initial forever #10 clk = ! clk ;

initial begin

// [1] ' req ' is True on 2nd posedge N then ' req ' is de - asserted just before Next posedge .

// ' ack ' is asserted at TIME : 49 !!

#20; // TIME:20

#9 ; req = 1 ; // TIME:29

#20 ; ack = 1 ; // TIME:49

#20 ; req = 0 ; // TIME:69

#5 ;

$finish() ;

end

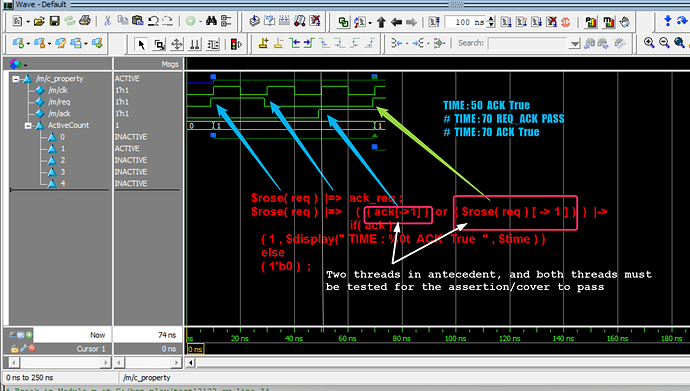

The O/P for +define+GO_TO ::

TIME : 50 PASS

TIME : 50 PASS // [ Q1 ] Why the 2nd Pass at TIME : 50 ??

The O/P for No +define i.e Via Non - Consequent Repetition ::

TIME : 70 FAIL

TIME : 70 FAIL // [ Q2 ] Why the Two Failures ??

I am trying to understand when would the antecedent True in both Cases .

So as you suggested the antecedent is equivalent to ::

// For +define+GO_TO ::

$rose( req ) [ ->1 ] is equivalent to :: ( ! $rose( req )[*0:$] ) ##1 $rose( req )

i.e ( ! $rose( req )[*0] or ! $rose( req ) [*1] or ! $rose( req ) [*2] or .... ) ##1 $rose( req )

Due to assertion being Multi - threaded ::

(1) First Thread starts on 1st posedge of Clock at TIME : 10

At 1st posedge at TIME : 10 , $rose( req ) is False . Hence ! $rose( req ) [ *1 ] is True !!

At 2nd posedge at TIME : 30 , $rose( req ) is True .

Hence antecedent is True at TIME : 30 !!

At 3rd posedge at TIME : 50 , as $rose( ack ) is True it's a Match and

for Thread 1 the assertion Passes at TIME : 50 !!

(2) Second Thread starts on 2nd posedge of Clock at TIME : 30

For the 1st posedge for Thread 2 at TIME : 30 ( 2nd posedge for the Simulation ) ::

( ! $rose( req )[*0] ) is True at TIME : 30

**[ Q3 ] So how is the antecedent True at TIME : 30 for Thread 2 ? As ##1 $rose( req ) is still not True**

// For No +define i.e Via Non - Consequent Repetition ::

Antecedent ' $rose( req ) [ = 1 ] ' is equivalent to ::

( ! $rose( req )[*0:$] ) ##1 $rose( req ) ##1 ( ! $rose( req )[*0:$] )

i.e ( ! $rose( req )[*0] or ! $rose( req ) [*1] or ... ) ##1 $rose( req ) ##1 ( ! $rose( req )[*0] or ! $rose( req ) [*1] or ... )

i.e ( Empty or ! $rose( req ) [*1] or ... ) ##1 $rose( req ) ##1 ( ! $rose( req )[*0] or ! $rose( req ) [*1] or ... )

At 1st posedge at TIME : 10 , $rose( req ) is False . Hence ( ! $rose( req ) [ *1 ] ) is True !!

At 2nd posedge at TIME : 30 , $rose( req ) is True .

At 3rd posedge at TIME : 50 , $rose( req ) is False .

Hence ( ! $rose( req ) [ *1 ] ) is True !!

As a result I believe Antecedent is True at TIME : 50 ( Please correct me if wrong )

At TIME : 70 , $rose( ack ) is False hence the Failure ( Please correct me if wrong )

[ Q4 ] But why does Thread2 FAIL at TIME : 70 ? When would the antecedent be True for Thread 2 ??