In reply to dave_59:

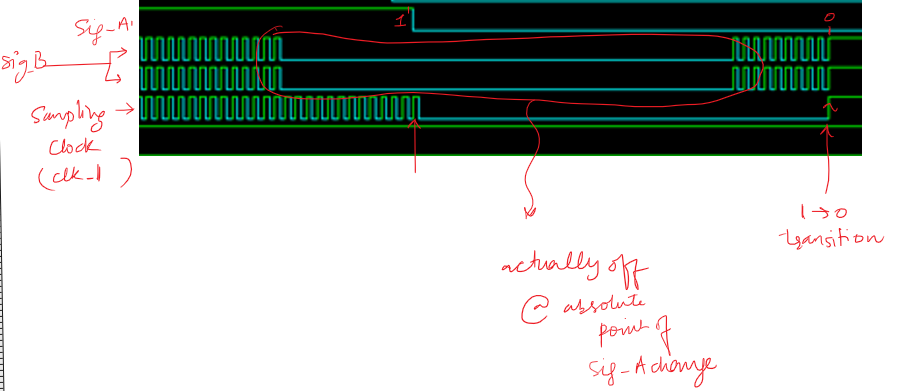

So at 3ns the assertion will sample the sig_a value to be 0 (in prepone region-just before the clock edge) and when the clocks return at 7ns the assertion will sample the value to be 1. This will be considered as a 0->1 change and check will be triggered. Is there any way where we can say like the last signal change was before the sampling clk gap so don’t consider it.

I thought something like this:

• Keepping a var that remembers the time of the last falling edge of the clock.

• Keeping a var that remembers the time of the last transition of the sig_a.

• Keeping a var sig_a_last signal that remembers what the sig_a was before the previous clock edge.

• At the rising edge of the clock, if sig_a!=sig_a_last, throw an assertion if the sig_a transition occurred outside the range of the last falling edge of the clock and the current time.

but I am not able to put/employ it in code exactly.