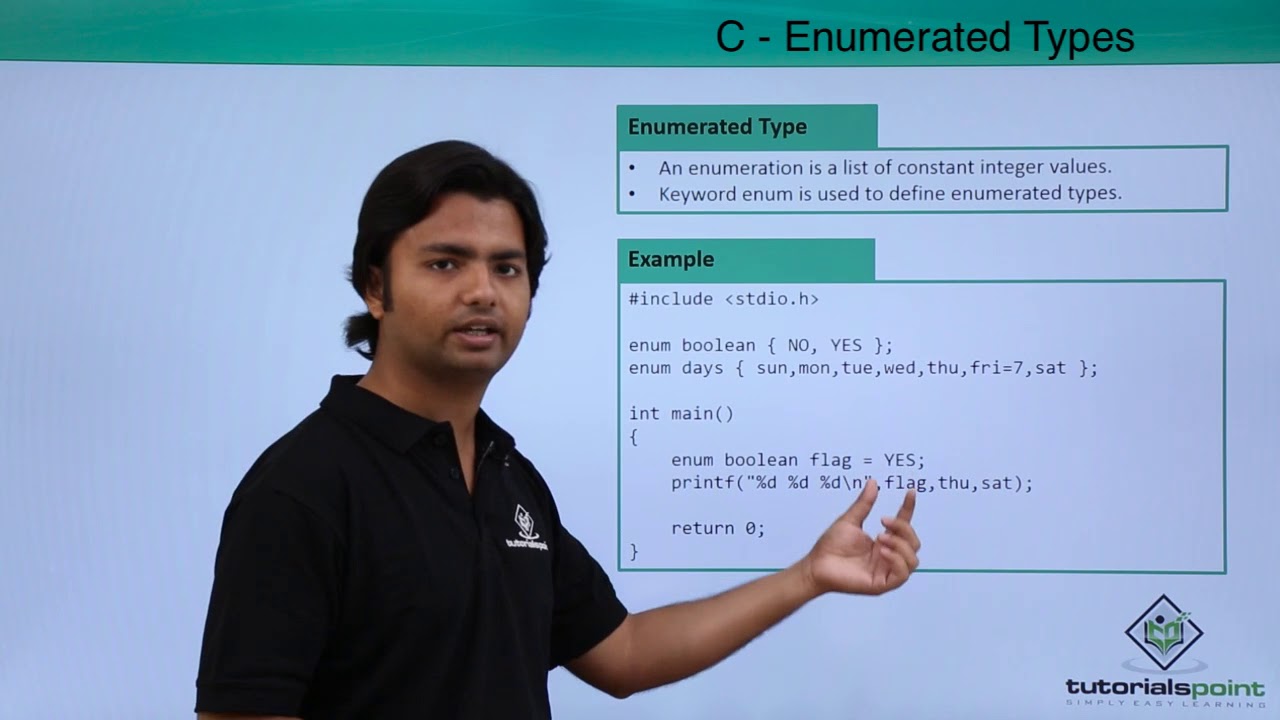

what is the meaning of enumarated data types and when to use it

In reply to Shivansh Bhardwaj:

In reply to Shivansh Bhardwaj:

See 1800’2017 6.19 Enumerations

The bottom line: It make the code mode readable. For example:

typedef enum {NOP, ADD, SUB, MULT, JMP, MOV, READ, WRITE, IDLE} instr_e;

typedef enum {FETCH, DECODE, EXECUTE} mode_e;

typedef enum {PC, IR1, IR2, REGA, REGB, MAR, REG_FILE, STK} resource_e;

instr_e instr;

if(instr==READ) ...

// You can assign values to these elements

// The values can be cast to integer types and increment from an initial value of 0. This can be overridden.

enum {bronze=3, silver, gold} medal; // silver=4, gold=5

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home.html

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats | Verification Academy

- Free books: Component Design by Example FREE BOOK: Component Design by Example … A Step-by-Step Process Using VHDL with UART as Vehicle | Verification Academy

Real Chip Design and Verification Using Verilog and VHDL($3) Amazon.com - Papers:

- Understanding the SVA Engine,

Verification Horizons - July 2020 | Verification Academy - SVA Alternative for Complex Assertions

Verification Horizons - March 2018 Issue | Verification Academy - SVA in a UVM Class-based Environment

SVA in a UVM Class-based Environment | Verification Horizons | Verification Academy

In reply to Shivansh Bhardwaj:

typedef enum{OKAY,BUSY,SPLIT,RETRY}resp_e

To indicate the different responses of protocols Ex:AHB