Hi experts,

i want to use different-different sequence in one test by using command line argument. So i use this approach in base_test as below code. on that code test_seq_s will take the sequence name as string from command line. got some error while use this approch

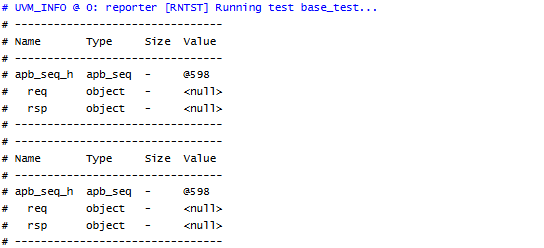

- while printing the obj and seq then got null for request and response.

added snapshot.

- while i am trying to get access the sequence member then got this error for obj and seq handle.

errors for obj: ** Error (suppressible): (vlog-13276) apb_basetest.svh(38:28): Could not find field/method name (data) in ‘obj’ of ‘obj.data’.

errors for seq: ** Error (suppressible): apb_basetest.svh(39): (vopt-7063) Failed to find ‘data’ in hierarchical name ‘seq.seq.data’.

code:

uvm_object obj;

uvm_factory factory;

uvm_sequence#(apb_pkt) seq;

string test_seq_s = "direct_vseq";

void'($value$plusargs("UVM_TEST_SEQ=%0s", test_seq_s));

factory = uvm_factory::get();

obj = factory.create_object_by_name(test_seq_s, "", {test_seq_s,"_h"});

if (obj == null) begin

factory.print(1);

`uvm_fatal(get_full_name(), $sformatf("could not create %0s seq", test_seq_s))

end

obj.print();

if (!$cast(seq, obj)) begin

`uvm_fatal(get_full_name(), $sformatf("cast failed - %0s is not a uvm_sequence", test_seq_s))

end

seq.print();

$display("Obj Data: %d",obj.data);

$display("Seq Data %d",seq.data);