In reply to rag123:

Spec: ARM_AMBA3_APB.pdf

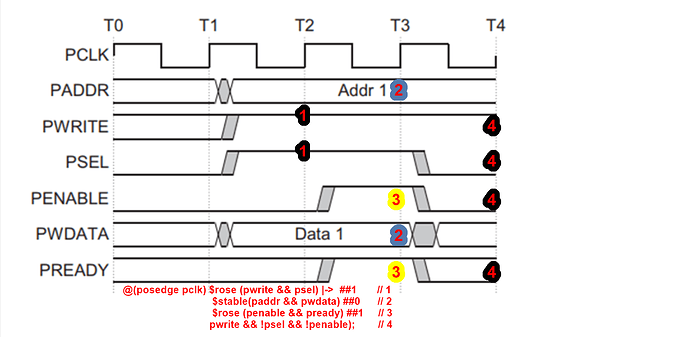

You are attempting to write an assertion for a Write transfer with no wait states. However the spec states that there are two types of write transfers:

• With no wait states

• With wait states.

The assertion you wrote, though incorrect, still needs a term in the antecedent to specify that this is a no wait transfer, else it will fail if more than one state.

@(posedge pclk) no_wait_write ##0 // generated by the testbench or slave

$rose (pwrite && psel) |-> ##1 // 1

$stable(paddr && pwdata) ##0 // 2 **ERROR in construct, see next posts

$rose (penable && pready) ##1 // 3

pwrite && !psel && !penable); // 4

The figure below shows the timing. The term no_wait_write ##0 is missing in the diagram.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home.html

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) Amazon.com - Papers:

- Understanding the SVA Engine,

Verification Horizons - SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment