Hi Dave,

suppose

consider this clk

which has 1ns =timeperiod

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…||....||…

signal c

…

here b toggles in duration when a is high ,assertion should show pass at 7ns ,if we write ancedent as $rose(a) or it wrote $fell(a) it show passs at 15ns.

scenario 2(fail)

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…

this is only scenario to fail, when both b or c remains low throughout the duration

it will show fail as explained above at 7ns or 15ns

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…|```````|…

here c toggles it will show pass similarly like first case

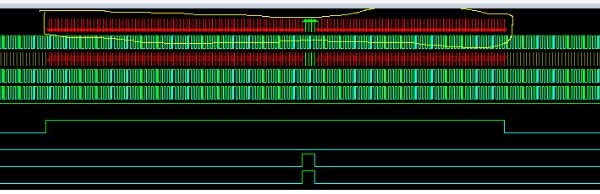

I need help to get the assertion to trigger only thread of pass or fail, in my case it triggeres at every posedge of clk

property p2;

@(posedge Clk) disable iff( (reset==0))

(a) |-> (b|c) within (a==1);

endproperty

P2: assert property(p2)

else begin

uvm_pkg::uvm_report_error(“assertions”, "Error on assertion " );

end

so the result is as follows

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…|```````|…

. .

. .

. .

. .

result

7=ns . ^ ^ ^ . 15ns

…|````````````````````````````````|…

8ns 9ns 11ns 12ns 13ns

so ^ represents pass at 9ns,10ns,11ns at c is high

but at 8ns,12ns,13ns,14ns it is low which is false condition so it triggere assertion false

but the requirement whether true or false we need only thread throughout checking?