I have several reactions to your ideas.

- On number of agents:> I’m considering 2 agents (one for write side and another for read side), can any one let me know their view when and how i can make a decision to used multiple agents/Virtual sequence(er), in this case is it right ??

I think that one agent is better because it is easier to maintain the actual count of the flags for full and empty flags. From my Real Chip Design and Verification book, below is a quick review of those flags, and how they are typically handled:

“Since full and empty flags are generated by pointers, where at least one of the pointers must be synchronized into a second clock domain, clock-cycle accurate assertion and de-assertion of full and empty flags is not completely possible. One FIFO design technique is to insure that a full or empty flag is asserted exactly when full or empty conditions occur, but de-asserting the flags might come a few clock cycles late. This is sometimes referred to as pessimistic full and empty flags.

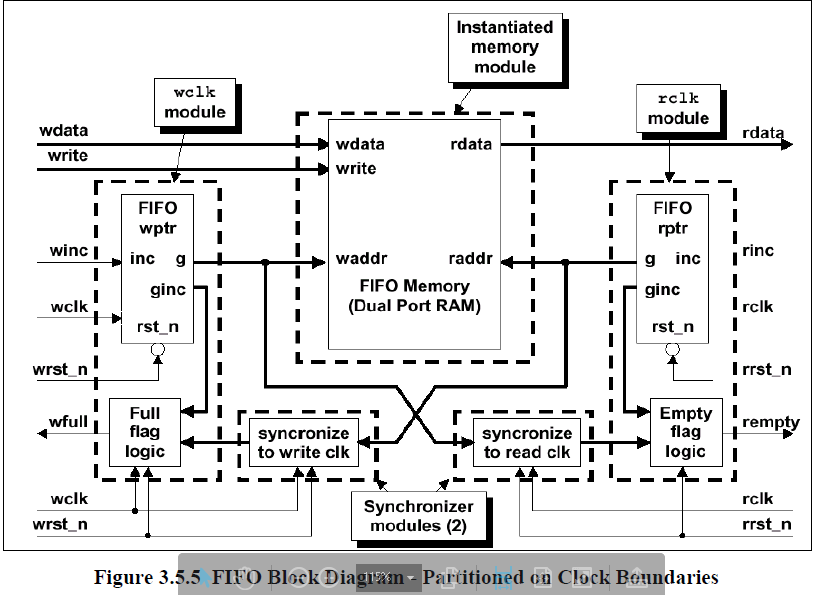

A pessimistic full flag is a full signal that is asserted immediately when a FIFO becomes full, but is de-asserted late (i.e., it is not de-asserted until a few read-clock cycles later). Because the write pointer does not have to be synchronized before testing for a full condition, the full flag will be asserted immediately when the FIFO goes full. The FIFO might not actually be completely full because the read pointer might have incremented (i.e., extracted data already), but the new read pointer value might not have been synchronized into the write clock domain. Using the block diagram shown in Figure 3.5.5, the READ pointer synchronized into the WRITE clock domain is always two WRITE clocks behind the actual READ pointer value, so the full flag might be asserted for two extra write clocks. This typically is not a problem since the full flag is simply holding off transmission of more data from the data sending source for two extra write clock cycles”.

- On your suggested scenarios, they look OK, but are you really using constrained-random tests or directed tests? Maybe constrained-random tests with various weighted constraints would be better.

- On verification, I would put that effort into the interface with SVA. I would copy from the class into the interface the values of those pointers for calculating the full/empty flags. See my White paper: “Using SVA for scoreboarding and TB designs”

http://SystemVerilog.us/papers/sva4scoreboarding.pdf

and a related issue at the Verification Academy the following paper

“Assertions Instead of FSMs/logic for Scoreboarding and Verification”

available in the verification-horizons October-2013-volume-9-issue-3

http://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3

and “SVA in a UVM Class-based Environment”

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115