Hi Forum Moderators,

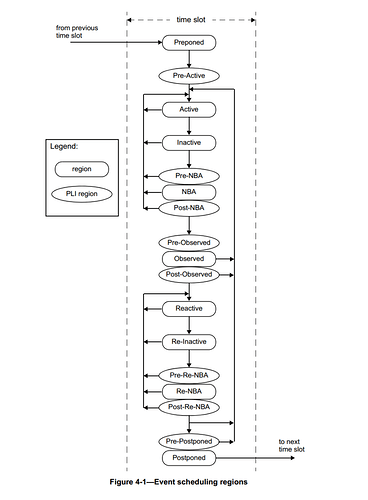

Figure 4-1 of SV LRM describes all the SV Regions

Note: There is no direct loopback from Reactive to Active.The loopback is from Re-NBA to Active.

I am trying examples that operate on

- Loopback from Active to Active

- Loopback from Reactive to Active

module tb;

bit clk ;

int c , val = 2;

always #5 clk = !clk;

always @(posedge clk) c <= c + 1; // Updated in NBA region

semaphore sema = new(0);

task automatic delay( int count );

if( count > 0 ) begin

repeat(count) @(posedge clk);

end

// For no +define :: What should the value of 'c' be in the next 2 statements ?

$display("Task completes at T:%0t with c == %0d",$time,c);

im: assert ( c == 3);

sema.put(1);

endtask

initial begin

`ifdef TASK

@(posedge clk);

delay(val);

`else

assert property( @(posedge clk) (1, delay( val )) );

`endif

sema.get(1);

$finish();

end

endmodule

(1) Using +define+TASK ::

- ‘delay’ gets called in active region at time:5 units.

- Event control @(posedge clk); would unblock in active region which is an example of loopback from Active to Active region.

- Immediate assertion would execute in Active region of T:25 using value of ‘c’ as 2

Hence fail_action block executes ( which is $error by default )

(2) Using no +define ::

- delay executes in Reactive region as it’s a subroutine called on match of sequence (1)

For (2) I am seeking inputs for the following ::

[Q1] Would the event control @(posedge clk) execute in Active region via loopback from Re-NBA to Active ?

[Q2] In which SV region would the $display() within ‘delay’ execute ?

[Q3] Would the Immediate assertion execute in Reactive region ( using value of ‘c’ as 3 ) ?

[Q4] Should the immediate assertion pass or fail at T:25 ? I observe different results across EDA tools