In reply to venkatasubbarao:

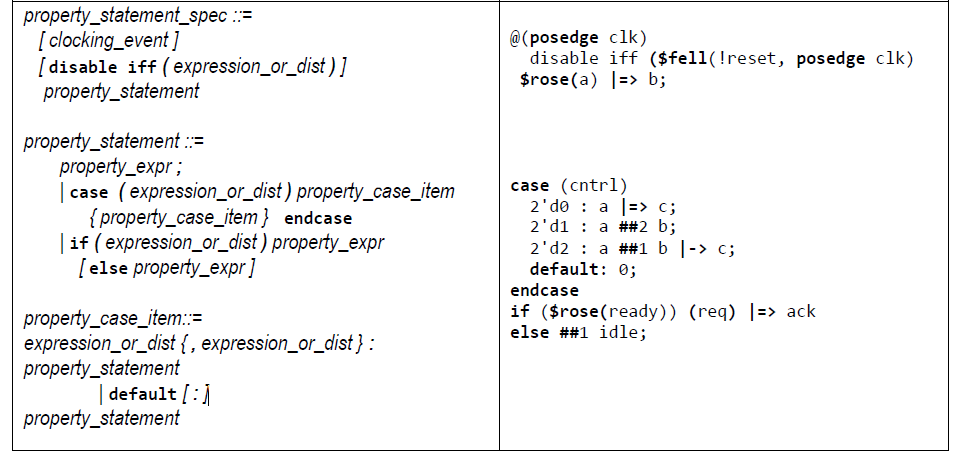

You need to look at the BNF syntax to know what is legal. From my book:

In general, I only write properties if they are reusable or if there is a need to use local variables, otherwise, I just write the assertions directly. I also prefer to use the default clocking and disable. I prefer smaller assertions and thus, would rewrite your assertions as:

default clocking @(posedge clk_in); endclocking

default disable iff (!resetn); // Use the logical negation instead of the bitwise invert

ap_NAME1: assert property(

##1 CK_EDGE_SEL && $fell(strb_in) |-> $stable(data)[*HOLD_TIME]);

ap_NAME2: assert property(##1 !CK_EDGE_SEL && $rose(strb_in) |->

$stable(data)[*HOLD_TIME]);

// No need for the ##0 in |-> ##0

// Need for the ##1 in antecedent because of the $stable that assumes that at the

// first clock edge $past(data) is the initial value of data. If that is not critical,

// then you do not need the ##1

On your “disable_assertion”, SVA provides assertion-control system tasks

4.2.4 Assertion-control system tasks from my book

SystemVerilog provides system tasks to control the evaluation of assertions (e.g., ON/OFF). In simulation, this can be very useful to disable property checking until the design under verification is in a stable initialized state. This feature allows the speedup in simulation when assertion checking is not needed and eliminates the need to use the disable iff (reset_n) to prevent false reporting when a user does not need to verify the assertions during initialization. The control system tasks are also useful for turning on/off assertions and cover statements based on the testbench, versus complex ifdefs or generates that evolve over time.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy

- http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

- “Using SVA for scoreboarding and TB designs”

http://systemverilog.us/papers/sva4scoreboarding.pdf - “Assertions Instead of FSMs/logic for Scoreboarding and Verification”

https://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3 - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment