Hi All,

Consider a concurrent assertion with an explicit clocking event ‘@(posedge) clk2’ embedded within an always procedural block with a different clocking event ‘@(posedge clk1)’ :: edalink

I have three questions related to it

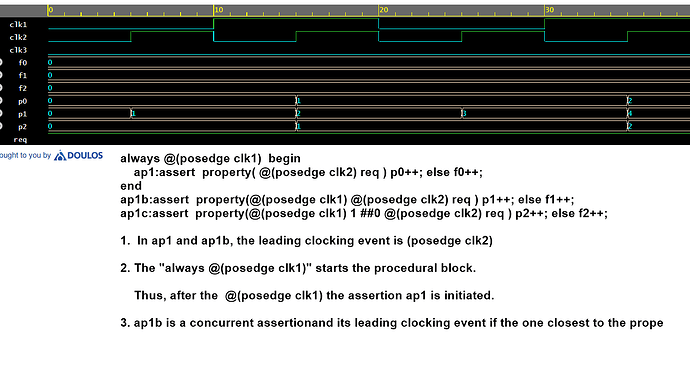

(Q1) Which clock would the concurrent assertion consider as leading clock ? Would it be equivalent to ::

ap1:assert property( @(posedge clk1) @(posedge clk2) req );

(Q2) How would the code work in the 3 cases ? ( I observe that the o/p differs across tools )

For (Q2) shouldn’t the concurrent assertion execute on the posedge of clk2 immediately following the posedge of clk1 ?

Here is my expectation ::

(a) For +define+M1 , as the always block is triggered at T:10 , 30 , 50

‘ap1’ should execute at T:15 , 35 , 55 respectively

(b) For +define+M2 , as the always block is triggered at T:05 , 15 , 25 , 35 , 45 , 55

‘ap1’ should execute at T:10 , 30 , 50 respectively

(c) For +define+M3 , as the always block is triggered at T:05 , 15 , 25 , 35 , 45 , 55

‘ap1’ should execute at T:05 , 15 , 25 , 35 , 45 , 55 respectively

(Q3) Would the addition of a default clocking block ( using @(posedge clk3) ), change anything ?