In reply to nimitz_class:

Given tht you did not provide a full model, I had to read between the line.

This is a model I created, and it works OK

module m;

realtime t1, t2, half_time_period;

bit clk1, clk2;

initial forever #10 clk1 = !clk1;

bit[3:0] state=4'b0010;

always @(posedge clk1) begin

t1 = $realtime;

@(negedge clk1)

t2 = $realtime - t1;

half_time_period = t2/2; // half time period of clock 1 divided by 2 to get 90 degree phase shifted time period

end

always @(posedge clk1) begin

realtime full;

full=2*half_time_period;

#half_time_period;

clk2 <= 1'b1;

#full;

clk2 <= 1'b0;

end

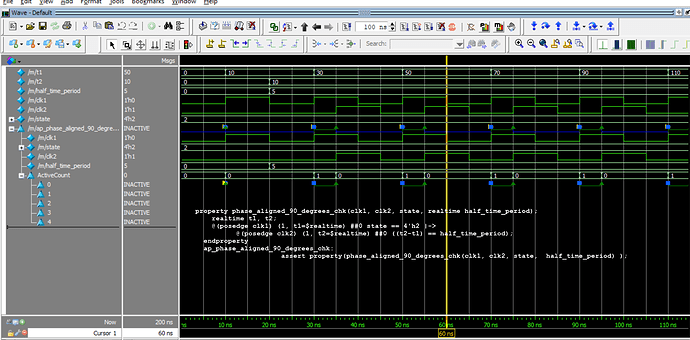

property phase_aligned_90_degrees_chk(clk1, clk2, state, realtime half_time_period);

realtime t1, t2;

@(posedge clk1) (1, t1=$realtime) ##0 state == 4'h2 |-> @(posedge clk2) (1, t2=$realtime) ##0 ((t2-t1) == half_time_period);

endproperty

ap_phase_aligned_90_degrees_chk: assert property(phase_aligned_90_degrees_chk(clk1, clk2, state, half_time_period) );

// I implemented it this way and see a mix of failures and success in the waveform. It's very confusing, kindly help.

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) https://rb.gy/cwy7nb - Papers:

- Understanding the SVA Engine,

Verification Horizons - SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment

Udemy courses by Srinivasan Venkataramanan (http://cvcblr.com/home.html)

https://www.udemy.com/course/sva-basic/

https://www.udemy.com/course/sv-pre-uvm/