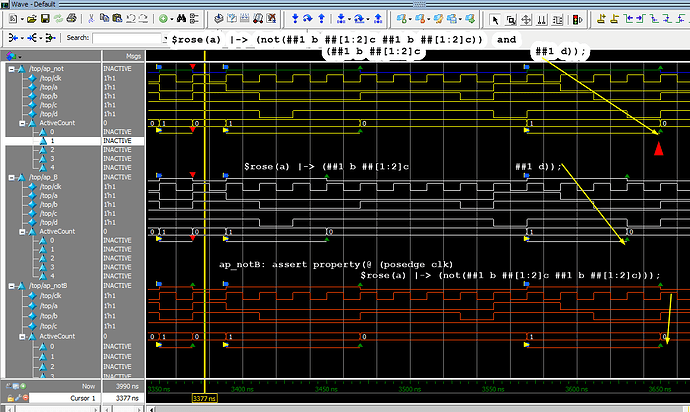

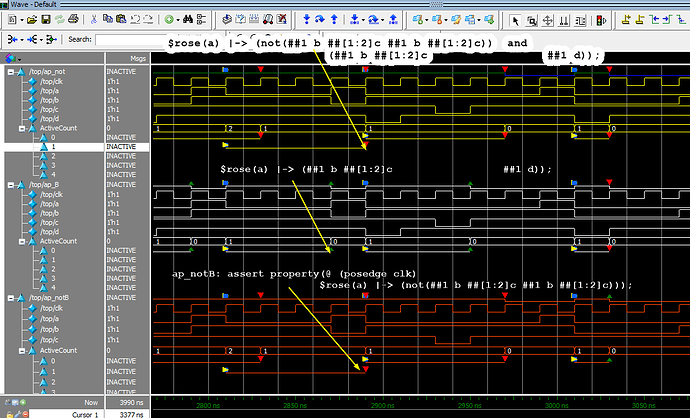

Hi, how can I build a sequence that it is true, only when another sequence has not happened. Let me put an example if I have this sequence:

|------/-/------|---------/-/---------|

A B C

(trigger) (seq1) (seq2)

How can I impose that between B and C there isn’t another B in between ?

sequence s_no_set_at_dst(set, set_dst, dst);

##[0:$] set ##0 set_dst != dst;

endsequence

sequence s_no_clr_at_dst(clr, clr_dst, dst);

##[0:$] clr ##0 clr_dst != dst;

endsequence

sequence s_no_set_within_rd(set, set_dst, re, re_dst, dst);

@(posedge clk_i) s_no_set_at_dst(set, set_dst, dst) within ##[0:$] (re ##0 re_dst == dst);

endsequence

sequence s_no_clr_within_rd(clr, clr_dst, re, re_dst, dst);

@(posedge clk_i) s_no_clr_at_dst(clr, clr_dst, dst) within ##[0:$] (re ##0 re_dst == dst);

endsequence

property p_clr_set0_rd (clr, clr_dst, set, set_dst, re, re_dst, out);

logic [5:0] _dst;

@(posedge clk_i) (clr, _dst = clr_dst) |->

##[1:$] (set ##0 set_dst == _dst)

##[1:$] ((re ##0 re_dst == _dst) and s_no_clr_within_rd(clr, clr_dst, re, re_dst, _dst) and s_set_within_rd(set, set_dst, re, re_dst, _dst))

##2 out == 1'b0;

endproperty

This is the code I have. Which is trying to detect if s_no_set_at_dst or s_no_clr_at_dst occurs while this sequence ##[0:$] (re ##0 re_dst == dst) is “waiting” to happen. But is not working.

Thanks