In reply to dave_59:

Dave,

It works for me too, but I have a followup question:

$changed ( expression [ , [ clocking_event ] ] )

// Is a 2d array an expression?

// Which one of these defines a 2d array as an "expression"?

expression ::= // 1800

primary

| unary_operator { attribute_instance } primary

| inc_or_dec_expression

| ( operator_assignment )

| expression binary_operator { attribute_instance } expression

| conditional_expression

| inside_expression

| tagged_union_expression

primary ::=

primary_literal

| [ class_qualifier | package_scope ] hierarchical_identifier select

| empty_unpacked_array_concatenation

| concatenation [ [ range_expression ] ]

| multiple_concatenation [ [ range_expression ] ]

| function_subroutine_call

| let_expression

| ( mintypmax_expression )

| cast

| assignment_pattern_expression

| streaming_concatenation

| sequence_method_call

| this41

| $42

| null

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk;

bit d2 [7:0][7:0];

initial forever #10 clk=!clk;

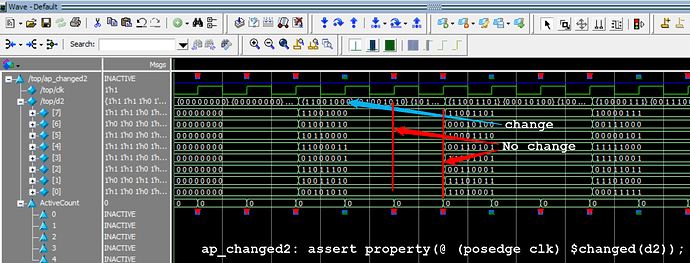

ap_changed2: assert property(@ (posedge clk) $changed(d2));

initial begin : ini1

repeat(10) begin :rpt1

repeat(3) @(posedge clk) #1;

if (!randomize (d2) ) `uvm_error("MYERR", "This is a randomize error");

end : rpt1

$stop;

end : ini1

endmodule

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home.html

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) https://rb.gy/cwy7nb - Papers:

- Understanding the SVA Engine,

Verification Horizons - SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment