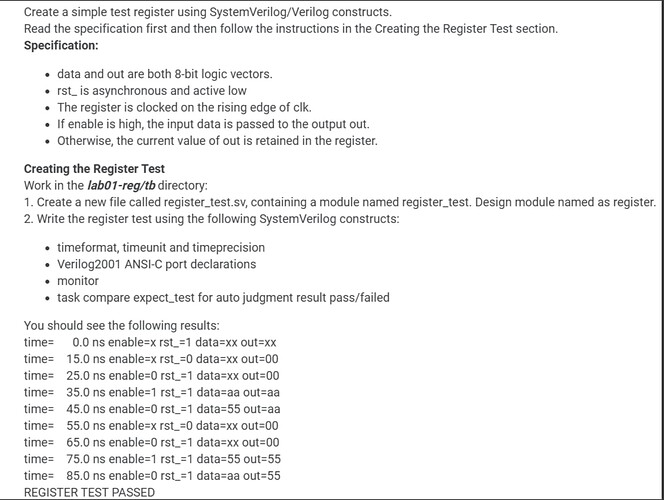

I am trying to design and test a dff using the requirement here.

`timescale 1ns/1ps

timeunit 1ns;

timeprecision 1ps;

module register (

input logic clk,

input logic rst_n, // active-low reset

input logic enable,

input logic [7:0] data,

output logic [7:0] out

);

// Sequential logic with async reset

always_ff @(posedge clk or negedge rst_n) begin

if (!rst_n)

out <= 8'h00; // reset clears output

else if (enable)

out <= data; // load input when enable = 1

else

out <= out; // hold previous value

end

endmodule

// Code your testbench here

// or browse Examples

// Code your testbench here

// or browse Examples

module register_test;

// DUT signals

logic clk;

logic rst_n;

logic enable;

logic [7:0] data;

logic [7:0] out;

// Instantiate DUT

register dut (

.clk (clk),

.rst_n (rst_n),

.enable (enable),

.data (data),

.out (out)

);

// Clock generation (10ns period)

initial begin

clk = 0;

forever #5 clk = ~clk;

end

// Monitor: display signals automatically

initial begin

$timeformat(-9, 1, " ns", 10);

$monitor("time=%t enable=%b rst_=%b data=%h out=%h",

$time, enable, rst_n, data, out);

end

// Task for comparison

task check_register_state;

if (out !== data)

$display("FAIL at %t: expected=%h, got=%h", ($time - 10), data, out);

else

$display("PASS at %t: out=%h", ($time - 10), out);

endtask

// Stimulus

initial begin

$dumpfile("dump.vcd");

$dumpvars(0, register_test);

// Initialize

// rst_n <= 1; enable <= 'x; data <= 'x; // 0

// #15 rst_n <= 0; expect_test; // 15

// #10 rst_n <= 1; enable <= 0; expect_test; // 25

// #10 enable <= 1; data <= 8'haa; expect_test; // 35

// #10 enable <= 0; data <= 8'h55; expect_test; // 45

// #10 rst_n <= 0; enable <= 'x; data <= 'x; expect_test; // 55

// #10 rst_n <= 1; enable <= 0; expect_test; // 65

// #10 enable <= 1; data <= 8'h55; expect_test; // 75

// #10 enable <= 0; data <= 8'haa; expect_test; // 85

// #10 $display("REGISTER TEST PASSED");

rst_n = 1; enable = 'x; data = 'x; // 0 ns

#15 rst_n = 0; // 15 ns

#10 check_register_state; // 25 ns

rst_n = 1; enable = 0;

#10 check_register_state; // 35 ns

enable = 1; data = 8'haa;

#10 check_register_state; // 45 ns

enable = 0; data = 8'h55;

#10 check_register_state; // 55 ns

rst_n = 0; enable = 'x; data = 'x;

#10 check_register_state; // 65 ns

rst_n = 1; enable = 0;

#10 check_register_state; // 75 ns

enable = 1; data = 8'h55;

#10 check_register_state; // 85 ns

enable = 0; data = 8'haa;

#10 check_register_state; // 95 ns

#10 $display("REGISTER TEST PASSED");

#1000;

$finish;

end

endmodule

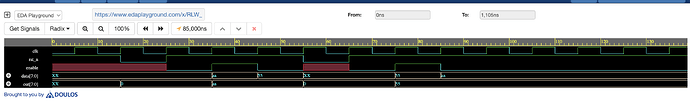

and log message I got seems to be true compared to the requirement above.

xcelium> run

time= 0.0 ns enable=x rst_=1 data=xx out=xx

time= 15.0 ns enable=x rst_=0 data=xx out=00

FAIL at 15.0 ns: expected=xx, got=00

time= 25.0 ns enable=0 rst_=1 data=xx out=00

FAIL at 25.0 ns: expected=xx, got=00

time= 35.0 ns enable=1 rst_=1 data=aa out=aa

PASS at 35.0 ns: out=aa

time= 45.0 ns enable=0 rst_=1 data=55 out=aa

FAIL at 45.0 ns: expected=55, got=aa

time= 55.0 ns enable=x rst_=0 data=xx out=00

FAIL at 55.0 ns: expected=xx, got=00

time= 65.0 ns enable=0 rst_=1 data=xx out=00

FAIL at 65.0 ns: expected=xx, got=00

time= 75.0 ns enable=1 rst_=1 data=55 out=55

PASS at 75.0 ns: out=55

time= 85.0 ns enable=0 rst_=1 data=aa out=55

FAIL at 85.0 ns: expected=aa, got=55

REGISTER TEST PASSED

My question is that if for example data = out = aa at the same timestep, it is not true according to the behavior of dff because out must be aa at the next cycle as I understand. Is this requirement true ?