In reply to Dilsya:

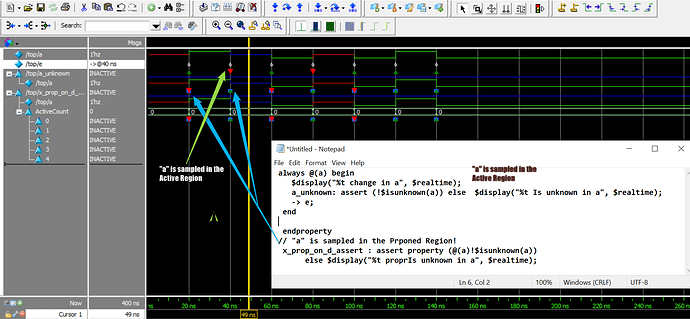

The issue you have with **assert property (@(a)!$isunknown(a))**is that “a” is sampled in the Preponed Region when “a” changes. Thus, if “a” goes from “1” to “X”, the sampling value is a “1” and thus $isunknown is false. You need the sampling to be in the Active Region.

Use the always with an immediate assertion.

module top;

logic a=1'bX;

event e;

always @(a) begin

$display("%t change in a", $realtime);

a_unknown: assert (!$isunknown(a)) else $display("%t Is unknown in a", $realtime);

-> e;

end

// "a" is sampled in the Preponed Region!

x_prop_on_d_assert : assert property (@(a)!$isunknown(a)) else $display("%t proprIs unknown in a", $realtime);;

initial begin

a=1'bX;

#20 a=1;

#20 a=1'bZ;

#20 a=0;

#20 a=1'bX;

#20 a=0;

#20 a=1;

#20 a=0;

#30;

end

endmodule

20 change in a

# 20 proprIs unknown in a

# 40 change in a

# 40 Is unknown in a

# 60 change in a

# 60 proprIs unknown in a

# 80 change in a

# 80 Is unknown in a

# 100 change in a

# 100 proprIs unknown in a

# 120 change in a

# 140 change in a

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact http://cvcblr.com/home

** SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

…

- SVA Package: Dynamic and range delays and repeats SVA: Package for dynamic and range delays and repeats - SystemVerilog - Verification Academy

- Free books: Component Design by Example https://rb.gy/9tcbhl

Real Chip Design and Verification Using Verilog and VHDL($3) https://rb.gy/cwy7nb - Papers:

- SVA Alternative for Complex Assertions

https://verificationacademy.com/news/verification-horizons-march-2018-issue - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment - Understanding the SVA Engine,

Verification Horizons