In reply to sanjay864u:

I am not sure I totally understand your question, but if you just want one occurrence of the assertion use the initial statement.

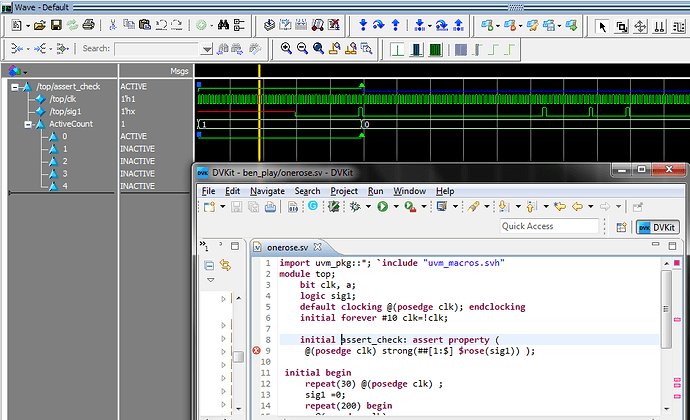

import uvm_pkg::*; `include "uvm_macros.svh"

module top;

bit clk, a;

logic sig1;

default clocking @(posedge clk); endclocking

initial forever #10 clk=!clk;

initial assert_check: assert property (

@(posedge clk) strong(##[1:$] $rose(sig1)) );

initial begin

repeat(30) @(posedge clk) ;

sig1 =0;

repeat(200) begin

@(posedge clk);

#2 if (!randomize(a, sig1) with

{ a dist {1'b1:=1, 1'b0:=3};

sig1 dist {1'b1:=1, 1'b0:=20};

}) `uvm_error("MYERR", "This is a randomize error")

end

$finish;

end

endmodule

simulation resuts:

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115