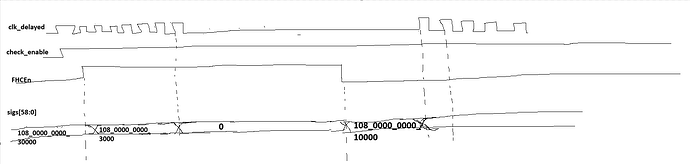

Following is my question, i have tried to represent in wave form fashion .

Question in writing:

1)@(posedge clk_delayed) disable iff reset=0 | check_enable=0

2) When ever FHCEn =1 is asserted in some cycles as shown i diagram check for sigs[58:0] = 0 while FHCEn remain 1 sigs should be 0 once FHCEn becomes zero stop checking

Following is my code attempted

property sigs_low_when_har_set_prop;

@(posedge clk_delayed) disable iff ((reset == 1'b0) || (check_enable == 1'b0) || (FHCEn == 1'b0))

$rose(FHCEn) |-> ##[4:8] (sigs === 0);

endproperty: sigs_low_when_harv_set_prop

NOte: If you notice when the FHCEn goes low there is no clock since its gated then i wonder how will the assertion notice this section to evaluate the property, because thats the point where sigs becoming zero… please make me understand this.

If you look at the image its exact prestation of my question, any suggestion thank you ?