In reply to ben@SystemVerilog.us:

In reply to rkg_:

Addressing your second question first

http://systemverilog.us/vf/rpt2.sv

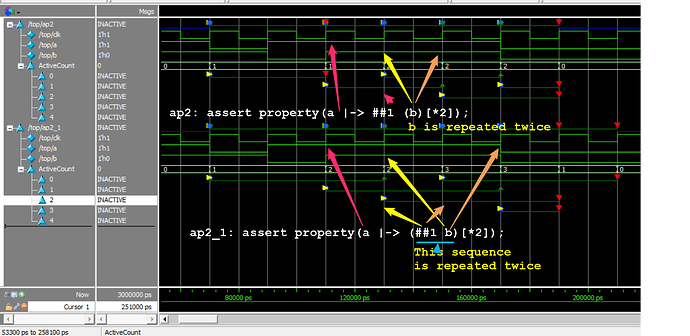

// After the |-> ##1 the sequence (b} is repeated twice

ap2: assert property(a |-> ##1 (b)[*2]);

// After the |-> the sequence (##1 b) is repeated twice

ap2_1: assert property(a |-> (##1 b)[*2]);

Hi Ben, I don’t get the difference. When I see both and try to rewrite the repetition operator I get

##1 b ##1 b

for both style. What am I missing?