I am a beginner to UVM and hence I am trying to verify APB protocol with standard spec.

I am able to write data perfectly with the waveforms being accurate.

But when trying to read the same data, it is not happening. (With the same testbench, I modified the DUT to a simple memory and I am able to read and write perfectly)

I have tried multiple ways.

Would there be any suggestions/any mandates to ensure before verifying read?

Below is my code for reference. Thank you.

In reply to Athulv:

In your monitor you do not have declared the virtual interface.

In reply to Athulv:

From the latest code you provide. Several things I want to mention:

- In sequence, you never set value for Pen. Your current sequence:

`uvm_do_with(req,{req.Pwrite==1;req.Psel==1;req.Paddr=='h50;})

`uvm_do_with(req,{req.Pwrite==0;req.Psel==1;req.Paddr=='h50;})

You need to add constraint for Pen as following:

`uvm_do_with(req,{Pwrite==1;Psel==1;Paddr=='h50;Pen == 1;})

`uvm_do_with(req,{Pwrite==0;Psel==1;Paddr=='h50;Pen == 1;})

- Your driver is not good. It doesn’t match with design behavior:

In your design, you check “Psel && !Pen” in SETUP state to change the state machine to W_ENABLE or R_ENABLE depending on “Pwrite”. However, in your driver, you always keep Psel and Pen signals at asserted state (level 1) after you completed the first transaction. That’s why, at the second transaction, the state machine never change state, it always keep SETUP state (because “Psel && !Pen” is never true).

Your current driver:

@(vif.m_dr);

vif.m_dr.Paddr<=trans.Paddr;

vif.m_dr.Pwrite<=trans.Pwrite;

vif.m_dr.Psel<=trans.Psel;

vif.m_dr.Pwdata<=trans.Pwdata;

//T2 clock cycle

@(vif.m_dr);

vif.m_dr.Pen<=trans.Pen;

You should deassert the Pen signal (and other signals as well) for the next transaction:

@(vif.m_dr);

vif.m_dr.Paddr<=trans.Paddr;

vif.m_dr.Pwrite<=trans.Pwrite;

vif.m_dr.Psel<=trans.Psel;

vif.m_dr.Pwdata<=trans.Pwdata;

//T2 clock cycle

@(vif.m_dr);

vif.m_dr.Pen<=trans.Pen;

// Deassert signals

@(vif.m_dr);

vif.m_dr.Pen<='b0;

vif.m_dr.Paddr<='b0;

vif.m_dr.Pwrite<='b0;

vif.m_dr.Psel<='b0;

vif.m_dr.Pwdata<='b0;

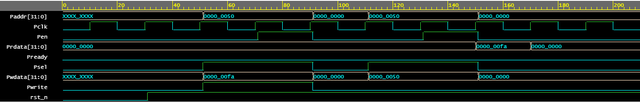

After modifying them, everything will be ok:

In reply to chris_le:

WOW! Perfect. Thanks a million Chris. You saved me. Thanks again.

In reply to chr_sue:

Thank you for the response. It’s working fine now. Thanks again.