In reply to Athulv:

From the latest code you provide. Several things I want to mention:

- In sequence, you never set value for Pen. Your current sequence:

`uvm_do_with(req,{req.Pwrite==1;req.Psel==1;req.Paddr=='h50;})

`uvm_do_with(req,{req.Pwrite==0;req.Psel==1;req.Paddr=='h50;})

You need to add constraint for Pen as following:

`uvm_do_with(req,{Pwrite==1;Psel==1;Paddr=='h50;Pen == 1;})

`uvm_do_with(req,{Pwrite==0;Psel==1;Paddr=='h50;Pen == 1;})

- Your driver is not good. It doesn’t match with design behavior:

In your design, you check “Psel && !Pen” in SETUP state to change the state machine to W_ENABLE or R_ENABLE depending on “Pwrite”. However, in your driver, you always keep Psel and Pen signals at asserted state (level 1) after you completed the first transaction. That’s why, at the second transaction, the state machine never change state, it always keep SETUP state (because “Psel && !Pen” is never true).

Your current driver:

@(vif.m_dr);

vif.m_dr.Paddr<=trans.Paddr;

vif.m_dr.Pwrite<=trans.Pwrite;

vif.m_dr.Psel<=trans.Psel;

vif.m_dr.Pwdata<=trans.Pwdata;

//T2 clock cycle

@(vif.m_dr);

vif.m_dr.Pen<=trans.Pen;

You should deassert the Pen signal (and other signals as well) for the next transaction:

@(vif.m_dr);

vif.m_dr.Paddr<=trans.Paddr;

vif.m_dr.Pwrite<=trans.Pwrite;

vif.m_dr.Psel<=trans.Psel;

vif.m_dr.Pwdata<=trans.Pwdata;

//T2 clock cycle

@(vif.m_dr);

vif.m_dr.Pen<=trans.Pen;

// Deassert signals

@(vif.m_dr);

vif.m_dr.Pen<='b0;

vif.m_dr.Paddr<='b0;

vif.m_dr.Pwrite<='b0;

vif.m_dr.Psel<='b0;

vif.m_dr.Pwdata<='b0;

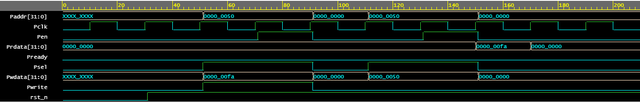

After modifying them, everything will be ok: