Hi,

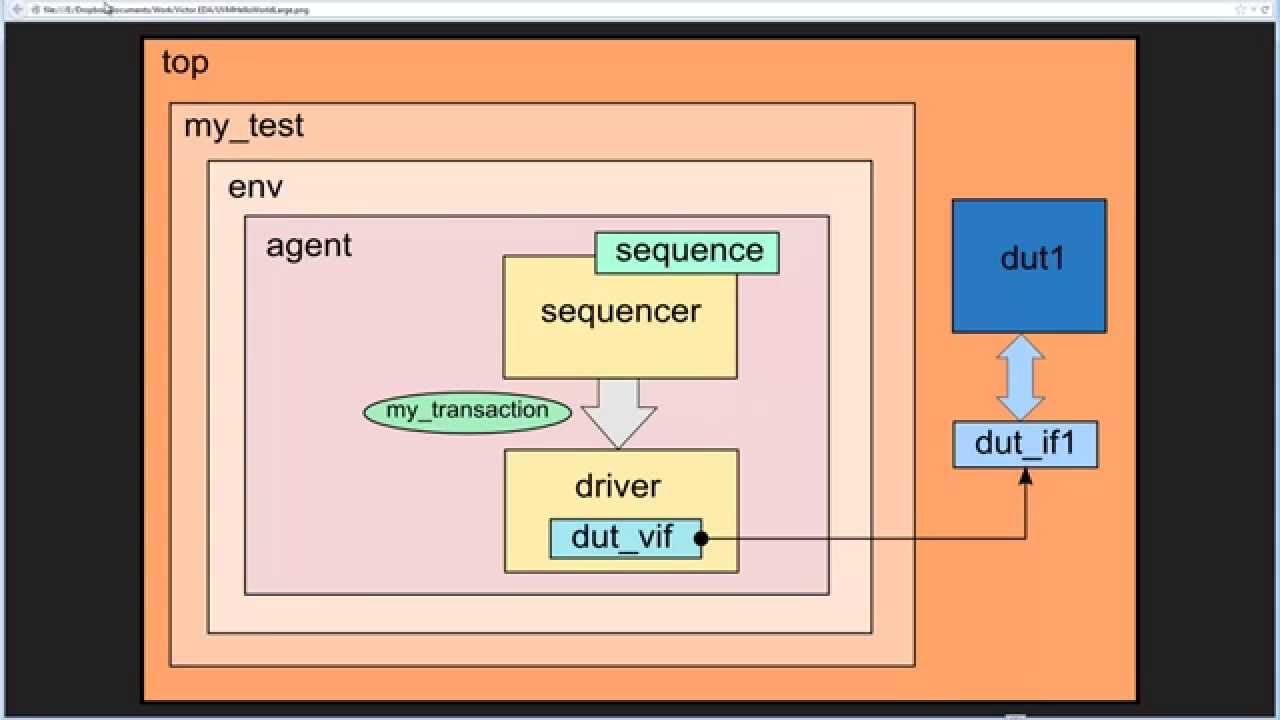

I am combining Simple UVM testbench and Hello world from EDA playground. I am using the binding mechanism which is in simple testbench in Hello world.

I am getting this warning during compilation, and when I simulate I get the error.

Please find the code attached along with the warning and error.

---------------------design.sv -------------------

`include “uvm_macros.svh”

module dut(

input clock,

input reset,

input cmd,

input [7:0] addr,

input [7:0] data

);

import uvm_pkg::*;

always @(posedge clock)

if (reset != 1) begin

`uvm_info(“DUT”,

$sformatf(“Received cmd=%b, addr=0x%2h, data=0x%2h”,

cmd, addr, data), UVM_MEDIUM)

end

endmodule

interface dut_if(

input bit clock,

input reset,

input cmd,

input [7:0] addr,

input [7:0] data

);

clocking cb @(posedge clock);

output reset;

output cmd;

output addr;

output data;

endclocking // cb

endinterface

bind dut dut_if dut_if12(

.clock(clock),

.reset(reset),

.cmd(cmd),

.addr(addr),

.data(data)

);

-------------- testbench.sv

/*******************************************

This is a basic UVM “Hello World” testbench.

Explanation of this testbench on YouTube:

*******************************************/

include "uvm_macros.svh" include “my_testbench_pkg.svh”

import uvm_pkg::;

import my_testbench_pkg::;

// The top module that contains the DUT and interface.

// This module starts the test.

module top;

bit clock;

dut dut1(.clock(clock));

// Clock generator

initial begin

clock = 0;

forever #5 clock = ~clock;

end

initial begin

// Place the interface into the UVM configuration database

uvm_config_db#(virtual dut_if)::set(null, “*”, “dut_if”, dut1.dut_if12);

// Start the test

run_test(“my_test”);

end

// Dump waves

initial begin

$dumpfile(“dump.vcd”);

$dumpvars(0, top);

end

endmodule

----------------- my driver.sv

class my_driver extends uvm_driver #(my_transaction);

`uvm_component_utils(my_driver)

virtual dut_if dut_vif;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

// Get interface reference from config database

if(!uvm_config_db#(virtual dut_if)::get(this, “”, “dut_if”, dut_vif)) begin

`uvm_error(“”, “uvm_config_db::get failed”)

end

endfunction

task run_phase(uvm_phase phase);

// First toggle reset

dut_vif.cb.reset <= 1;

@(dut_vif.cb);

#1;

dut_vif.cb.reset <= 0;

// Now drive normal traffic

forever begin

seq_item_port.get_next_item(req);

// Wiggle pins of DUT

dut_vif.cb.cmd <= req.cmd;

dut_vif.cb.addr <= req.addr;

dut_vif.cb.data <= req.data;

@(dut_vif.cb);

seq_item_port.item_done();

end

endtask

endclass: my_driver

Warning during compilation

** Warning: (vlog-2650) ‘bind’ found in compilation unit scope. Please use -cuname to ensure that ‘bind’ gets elaborated.

Error during simulation

arning: (vsim-3008) testbench.sv(30): [CNNODP] - Component name (dut_if12) is not on a downward path.