Hello,

I was wondering whether it is possible to access a register/memory/register block. For example, if I could access it using a hierarchical path that’s concatenated and also an absolute path. For example, a register

add_hdl_path_slice("reg_1", 0, 32);

add_hdl_path_slice("top.dut.reg_1", 0, 32);

Does the parameter kind have anything to do with this?

Thank you all!

In reply to polivka:

Why would want to provide 2 ways to describe the path to the same register? A register only has a single hierarchical path. What are you trying to accomplish?

In reply to warnerrs:

I want to have a backdoor that’s implemented without any concern for the actual DUT implementation. As in the hierarchy of my RAL/register model does not, but could, correspond to the actual hierarchy on the DUT. I know I can add the entire hierarchy to the hdl path slice, as long as it connects to the top of the testbench, but I want to avoid this because it could be prone to mistakes.

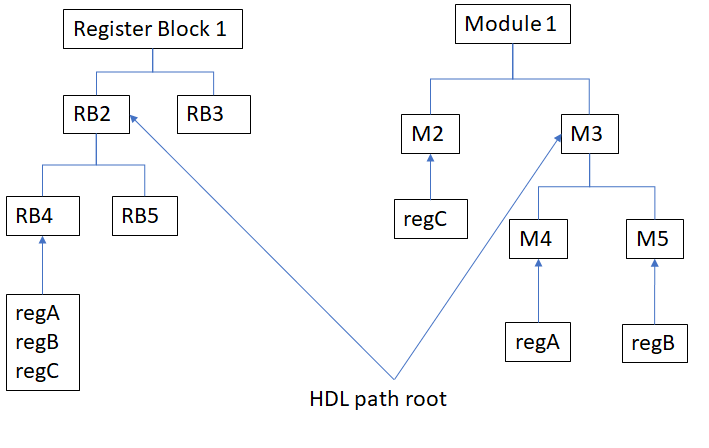

The following picture could be good example. It’s not a problem to give a hierarchical path for the regA (M4.fieldA) and regB (M5.fieldB), regC is inaccessible because it’s not below M3 and anything like (Module1.M2.fieldC) for the path slice will not work. Is there a way to get around this? Is there any additional documentation or tutorials besides the uvm cookbook from verification academy?

Can someone take a look at this , I am also facing a similar issue .

A register has a single instance path. Having multiple paths to a physical register does not make sense, unless you are using some quantum entanglement. That won’t be in SystemVerilog until 2033 at the earliest. :-)