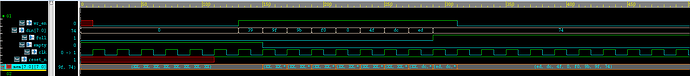

wr_en is high for one extra clock cycle even if fifo full is asserted as a result of which buffer is getting over-flowed

//dut write logic

assign wr_loc = wr_ptr[ADDR_WIDTH-1 : 0];

always @(posedge clk) begin

if (wr_en) begin

mem[wr_loc] <= din;

end

end

always @(posedge clk) begin

if(!reset_n) begin

wr_ptr <= 'h0;

end

else begin

if(wr_en & (~full))begin

wr_ptr <= wr_ptr+1;

end

end

end

// tb write logic

always @(posedge clk) begin

fifo_wr_en <= 0;

if (reset_n & (~fifo_full)) begin

fifo_wr_en <= 1;

trans_in <= $urandom;

end

end