I am starting this built in sequence, at the end of the sequence I am getting 3 error for 3 registers. One of them is

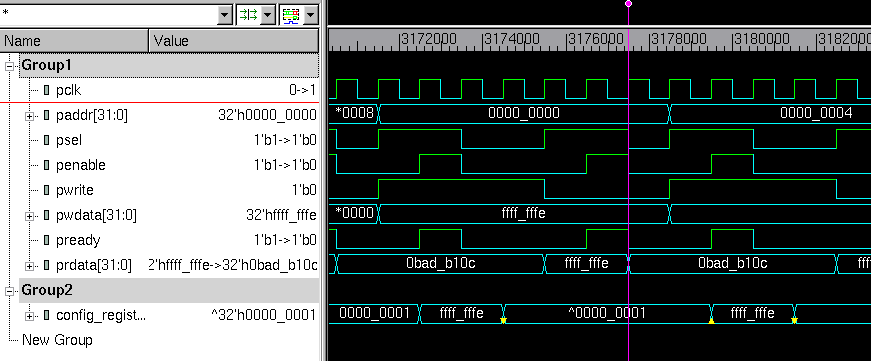

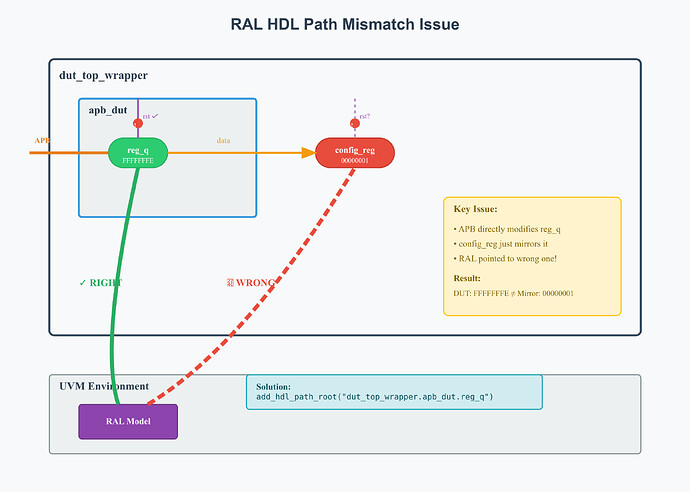

regmodel.REG_0" value read from DUT (0x00000000fffffffe) does not match mirrored value (0x0000000000000001)

the reset value to that register is all 0000001. how is this reset getting applied in between? I have called regmode.reset(); inside run_phase of testcase before starting the sequence.

I feel there is some synchronization issue. but don’t know exactly what.

If I assume reset is being applied by sequence, then dut read value should be 00000001 and mirrored value should be 00000001. but here dut read value is not 00000001. Correct me if I am understanding wrong.

Anyone knows the answer?