We need to check when a=1 ,suppose at 3 ns we should start checking and if falls at 15 ns we should continue checking.

step 2 : once a is high start checking for either b or c is high during a remains high

step 3 : if they found even single or many times that b or c is high , assertion should show success only once. and that too at the fell of a.(15ns

step 4: if c or b is newer high during that period ,only one fail will be reported no multiple threads required , one fail will be reported at fell of a.(15ns

.

note : I have tried intersect, within not working I mean we need only one thread .as requirement

Hi Ben,

first code try using within

property p2;

@(posedge Clk) disable iff( (reset==0))

(a) |-> lock3 within (a==1);

endproperty

P2: assert property(p2)

else begin

uvm_pkg::uvm_report_error(“assertions”, "Error on assertion " );

end

logic lock3=0;

always@(posedge Clk)

begin

if(Reset==0| a==0 )

lock3<=0;

else

lock3<= (b| c);

end

second using normal $fell as i needed only one thread result

property p;

@(posedge SdpClk) disable iff(Reset==0 )

$fell(a) |-> lock3;

endproperty

P_check: assert property(p)

else begin

uvm_pkg::uvm_report_error(“assertions”, "Error on assertion " );

end

My code : where i tried to assign lock4 with value with whenever b or c is high lock4 is high, and we need to trigger the result of assertion at fell of a .

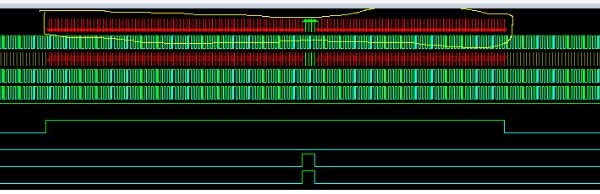

wave result:

first code:

The one marked in yellow is not needed as result I need result as one thread either pass or fail.

For that I have written a code but it fails.

As when i check rose(a) or fell( a) it becomes edge trigger but i need to check throughout the level a is high, but return the result only once as pass or fail.

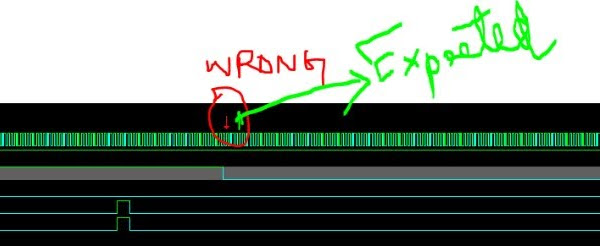

expected snap

second code:

Hope it clears all2, in first snap though i am able to get the edge where i see either b or c is passing it created thousands of false threads and we need one pass or fail.

consider this

consider this

signal a

/,/

t=7ns t=15ns

signal b

…/…/…

t=12ns

consider them as high edge

signalc

…

result would be pass

/…/

∆

pass at 15 ns

fail condition

signal a

…/ /…

signal b

…

signal c

…

as not once b or c is high when a is high it should show fails at 15 ns

more clearly this

consider this clk

which has 1ns =timeperiod

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…||....||…

signal c

…

here b toggles in duration when a is high ,assertion should show pass at 7ns ,if we write ancedent as $rose(a) or it wrote $fell(a) it show passs at 15ns.

scenario 2(fail)

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…

this is only scenario to fail, when both b or c remains low throughout the duration

it will show fail as explained above at 7ns or 15ns

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…|```````|…

here c toggles it will show pass similarly like first case

I need help to get the assertion to trigger only thread of pass or fail, in my case it triggeres at every posedge of clk

property p2;

@(posedge Clk) disable iff( (reset==0))

(a) |-> (b|c) within (a==1);

endproperty

P2: assert property(p2)

else begin

uvm_pkg::uvm_report_error(“assertions”, "Error on assertion " );

end

so the result is as follows

a signal

7=ns 15ns

…|````````````````````````````````|…

signal b

…

signal c

…|```````|…

. .

. .

. .

. .

result . .

. .

7=ns . ^ ^ ^ . 15ns

…|````````````````````````````````|…

8ns 9ns 11ns 12ns 13ns

so ^ represents pass at 9ns,10ns,11ns as c is high

but at 8ns,12ns,13ns,14ns it is that both b and c is low which is false condition so it triggers assertion false but it should not as the duration when a is high from 7ns to 15ns c goes high from 9ns to 11ns so our assertion condition is fulfilled.

so the end result requirement will be whether true or false we need only one thread throughout checking?

Please help