SystemVerilog LRM: page #244

b ##1 a[*0:1] ##2 c#2 c) or (b ##1 a ##2 c)

Question: if b goes high , then after 1 clock a can or can not be there, then after 2 clocks c should b high. (even if a is high for zero cycle or one cycle, ##1 is there between checking of b and a)

so how come it is equivalent to (b ##2 c)? shouldn’t it be (b ##3 c)?

Thank you in advance.

user49

February 3, 2016, 7:53am

2

In reply to vickydhudashia :

(b ##1 a[*0:1] ##2 c) is equivalent to

(b ##1 a[*0] ##2 c) or (b ##1 a[*1] ##2 c)

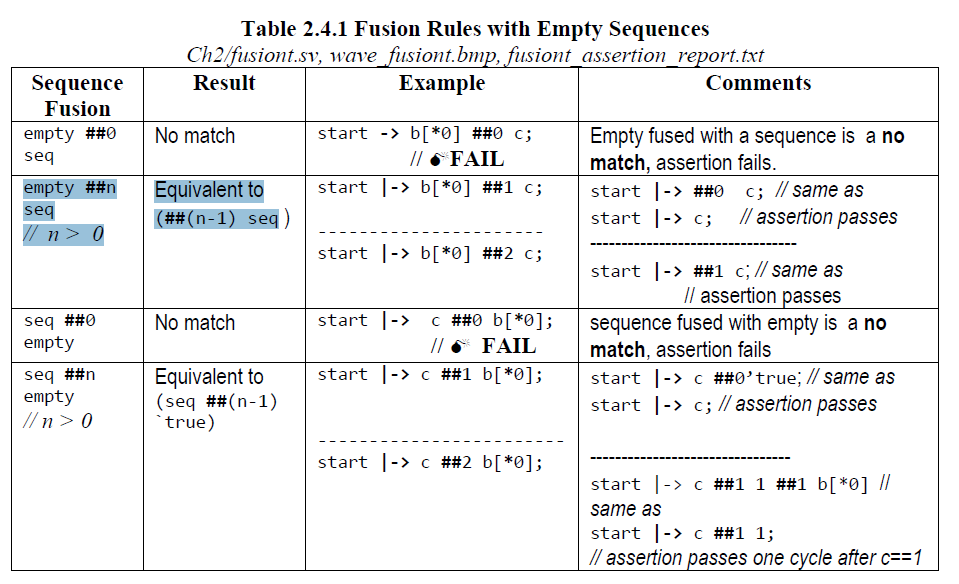

Now a[*0] is an empty match, and the rules of empty are as follows#n seq // with n > 0

(b ##1 a[*0] ##2 c) is equivalent to

(b ##1 ##1 c)

The LRM is correct, SystemVerilog LRM: page #244

b ##1 a[*0:1] ##2 c

is equivalent to

(b ##2 c) or (b ##1 a ##2 c)

From my book:

Ben Cohenhttp://www.systemverilog.us/ ben@systemverilog.us

SystemVerilog Assertions Handbook 4th Edition, 2016 ISBN 978-1518681448

A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

Component Design by Example ", 2001 ISBN 0-9705394-0-1

VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

In reply to ben@SystemVerilog.us :

Thank you Ben , This cleared my doubt.