Hi all

any there sva cookbooks or article that show how to write sva in good coding styles?

thanks a lot!

In reply to peter:

Hi all

any there sva cookbooks or article that show how to write sva in good coding styles?

thanks a lot!

“Style” is a very fluid word as it involves many disciplines. In my SVA Handbook 4th Edition chapter 8, SystemVerilog Assertions Guidelines, addresses that topic (see the TOC). There is style in:

-

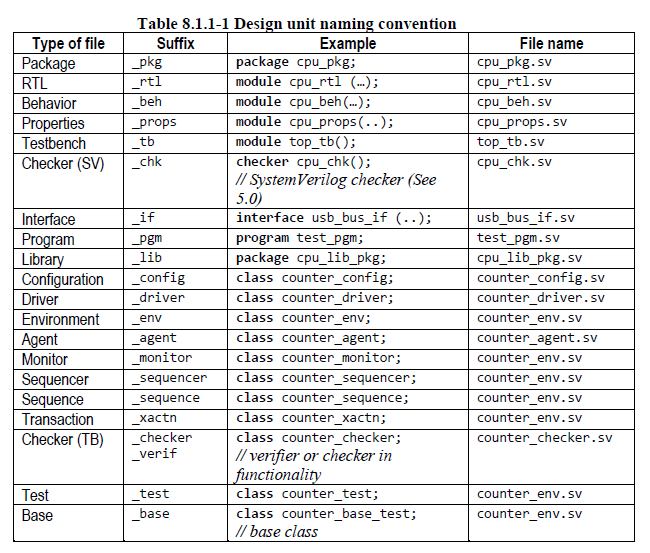

Naming convention, as that helps in the identity of variables, type of construct, etc. For example

-

Separating properties from assertions: Unless there is a lot of reuse, and if the property has no local variables, I prefer to just use the assertion statement without the property declaration.

-

Use of defaults: I generally like the default clocking and disable.

-

Writing the antecedents: This is a good example of what NOT TO DO in style

Assertion causes sim crash - SystemVerilog - Verification Academy -

Where to put the assertions in the DUT? in a separate module bound to the DUT?, in SystemVerilog checker inline or bound to the DUT an/or interface?

-

Approaching the requirements: Multiple small assertions? Approaching the requirements from different levels? etc.

-

[b]Correctness/completion:[/b] It is very easy to write assertions that can never fail, or never succeed; this must be avoided.

-

Using alternate approaches to SVA: See my white papers with the links below my signature.

-

Bad properties: Avoid vacuous properties, and contradictory properties

-

Use of unsized additions using +1 versus +1’b1,

-

Adding Environmental properties: They represent properties that are required for a proper functionality of the design when it is embedded into a larger design. For example:

- Never PUSH while the FIFO FULL flag is asserted.

- Never POP while the FIFO EMPTY flag is asserted.

- Never a DMA interrupt until done of DMA transfer

…

- Process of writing properties and assertions: That includes Identify the characteristics of the design, Partition complex assertions using named sequences, etc.

- Handling dynamic delays and repeats: see my white papers http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact Home - My cvcblr

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy

- http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

- “Using SVA for scoreboarding and TB designs”

http://systemverilog.us/papers/sva4scoreboarding.pdf - “Assertions Instead of FSMs/logic for Scoreboarding and Verification”

https://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3 - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment

In reply to ben@SystemVerilog.us:

Thanks!!