I came across this following paragraph in Systemverilog LRM

“Abstract classes may be extended to further abstract classes, but all pure virtual methods shall have overridden implementations in order to be extended by a non-abstract class.

By having implementations for all its methods, the class is complete and may now be constructed. Any class may be extended into an abstract class, and may provide additional or overridden pure virtual methods.”

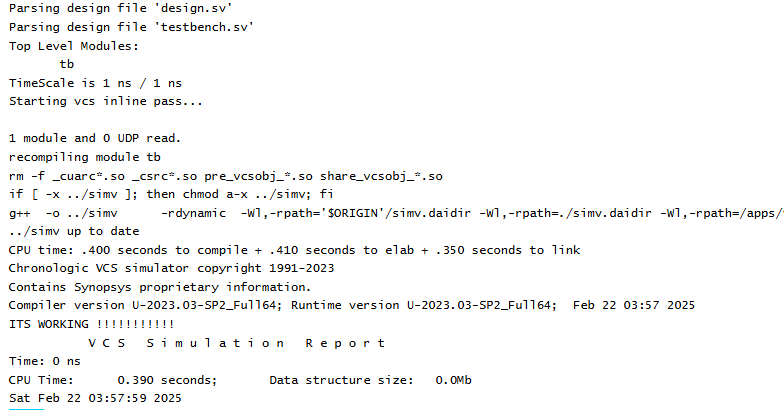

Notice that it says the extended abstract classes should provide implementation for the pure virutal methods. but i wrote a program in which i didnt provide impmentation for the pure virtual method in the extended abstract class , but it is still working . Can anyone help me with this. Am i interpreting it wrong or is there some thing wrong with it ? The following is my code

// BASE ABSTRACT CLASS

virtual class base ;

int a = 7;

pure virtual function void display();

endclass

// CHILD ABSTRACT CLASS

virtual class child extends base;

int a = 4;

pure virtual function void display();

endclass

// GRANDCHILD CLASS EXTENDED FROM CHILD ABSTRACT CLASS

class grandchild extends child;

int a = 8;

function void display();

$display("ITS WORKING !!!!!!!!!!!");

endfunction

endclass

// MODULE TB

module tb;

grandchild g1 ;

initial

begin

g1 = new;

g1.display();

end

endmodule

It is working with all the simulators in the EDA playground