In reply to pawan:

If you have issues in the setup and hold, and when signals are sampled, consider using clocking blocks. From my SVA Handbook 4th Edition

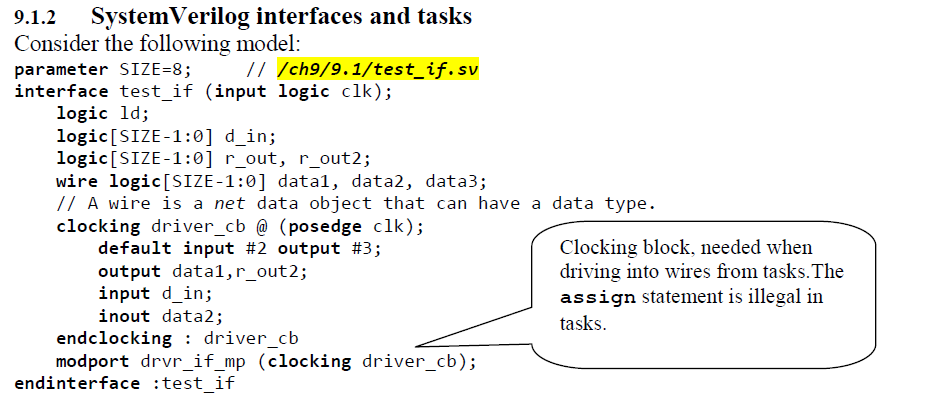

SystemVerilog also allows for the specification of input and output skews. Input (or inout) signals are sampled at the designated clock event. If an input skew is specified then the signal is sampled at skew setup time units before the clock event. Similarly, output (or inout) signals are driven skew hold simulation time units after the corresponding clock event. An example of a skew definition is shown below: