I am trying to understand how clocking block avoids the race condition between testbench(TB) and DUT. I am aware that clocking block construct introduces skews. But I can’t visualize how these skews avoid the race condition between TB and DUT. Can anyone elaborate with an example/scenario, to visualize this type of race condition in testbench? Thanks for your time in advance.

In reply to rakesh2learn:

I am trying to understand how clocking block avoids the race condition between testbench(TB) and DUT. I am aware that clocking block construct introduces skews. But I can’t visualize how these skews avoid the race condition between TB and DUT. Can anyone elaborate with an example/scenario, to visualize this type of race condition in testbench? Thanks for your time in advance.

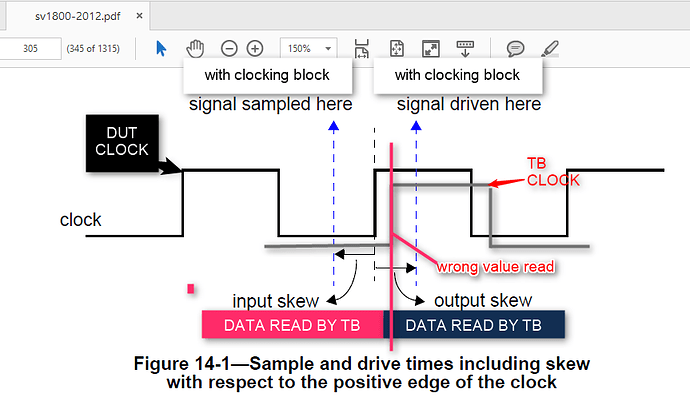

- 1) The clocking block enforces a time when signals are sampled. For example, assume a clock period of 10ns, and a clock jitter of 1ns between the testbench clock and the internal gate-level clock of the design. This uncertainty is caused by the internal delay of the DUT’s clock drivers and tree. (The 1 ns is excessive, but am using this number to make a point). That jitter can cause sampling problems, unless you can adjust the sampling time. Below is an annotated image of the problem, based on what is in 1800

-

- S similar argument can be made about inputs into the DUT

- 2)Clocking block, needed when driving into wires from tasks.The assign statement is illegal in classes. The reasons the clocking block works is exaplained in 1800. 1800-2012, section 14.3 Clocking block declaration states:

- A clockvar whose clocking direction is inout shall behave as if it were two clockvars, one input and one output, having the same name and the same clocking signal.

- Reading the value of such an inout clockvar shall be equivalent to reading the corresponding input clockvar.

- Writing to such an inout clockvar shall be equivalent to writing to the corresponding output clockvar

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

In reply to ben@SystemVerilog.us:

Hi Ben,

I tried to understand how “race condition” can happen in testbench-design, and I found this post. I am not sure I understand in your example picture. In the picture, why TB clock goes after DUT clock? Normally, we use TB to drive clock/reset signal to DUT. TB clock should be asserted before DUT clock (incase we have clock delay/slew), right?

Thanks.

In the picture, why TB clock goes after DUT clock?

It does not. The clocking block uses the main clock. What the clocking does is controlling the sampling of the data for reading and writing

The interface

clocking driver_cb @ (posedge clk);

output rst_n, data_in, ld, kind_cp;

input counter;

endclocking : driver_cb

clocking mon_cb @ (posedge clk);

input rst_n, data_in, ld, kind_cp;

input counter;

endclocking : mon_cb

modport drvr_if_mp (clocking driver_cb);

modport mon_if_mp (clocking mon_cb);

....

Driver does this

task load_task(int data);

this.vif.driver_cb.data_in <= data;

this.vif.driver_cb.rst_n <= 1'b1;

this.vif.driver_cb.ld <= 1'b1;

@(this.vif.driver_cb)this.vif.driver_cb.ld <= 1'b0;

endtask : load_task

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

For training, consulting, services: contact Home - My cvcblr

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 978-1539769712

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115

- VF Horizons:PAPER: SVA Alternative for Complex Assertions - SystemVerilog - Verification Academy

- http://systemverilog.us/vf/SolvingComplexUsersAssertions.pdf

- “Using SVA for scoreboarding and TB designs”

http://systemverilog.us/papers/sva4scoreboarding.pdf - “Assertions Instead of FSMs/logic for Scoreboarding and Verification”

https://verificationacademy.com/verification-horizons/october-2013-volume-9-issue-3 - SVA in a UVM Class-based Environment

https://verificationacademy.com/verification-horizons/february-2013-volume-9-issue-1/SVA-in-a-UVM-Class-based-Environment