In reply to puranik.sunil@tcs.com:

Referring to the discussion above on series “aaa” my question was that if there assertion,

a1: assert property (@(posedge clk) a[*1:$] |-> p)

then for example, for input pattern aa (meaning a==1 ##1 a==1in first two clocks, p has to be true in both the clocks for assertion to be true, for pattern aaa, p has to be true in all three clocks, for pattern aaaa, p has to be true in all 4 clocks… etc. Same holds for all n till end of simulation.

[Ben] That part is correct. However, for a pattern like

attempt m n k t y

cycle 1 2 3 4 5

a== 1 1 1 0 X . ..

p== 1 1 1 X X

assertion

4 attempt m S A A P // result for attempt m, thread 4 @ cycle 4 is vacuous true

// Thus, since for cycle 1, 2, 3 a==1 and p==1 and all possible threads of the antecedent were exercised with no failure, the assertion is a pass. NOTE: vacuous true is success.

However, since you have at least one nonvacuous true of the property, the property is a

nonvacuous true and the assertion is a pass. Once you have a zero in "a" like aaa!a all other threads after that !a are vacuous passes. Notation

S== started

A == active

P == PASS

F == FAIL

V == vacuous

--------------------------------------------

CONSIDER THIS case

attempt m n k t y

cycle 1 2 3 4 5

a== 1 1 1 0 X . ..

p== 1 1 0 X X

assertion

4 attempt m S A F - // result for attempt m, thread 3 @ cycle 3 is FAIL

so does it mean

a1: assert property (@(posedge clk) a[*1:$] |-> p)

is same as

a1: assert property (@(posedge clk) a |-> p)

NO. CONSIDER THIS case

attempt m n k t y

cycle 1 2 3 4 5

a== 1 1 1 0 X . ..

p== 1 1 0 X X

assertion a[*1:$] |-> p)

4 attempt m S A F - // result for attempt m thread 3 @ cycle 3 is FAIL

--

assertion a |-> p

4 attempt m P -------------

4 attempt n - P ------------

4 attempt k ---------F -------

4 attempt t ------------V // vacuous true, vacuous result

// Remember that ALL threads of antecedent must be tested. Simulator may optimize; e.g., for a[*1:$], any occurrence of a==0 means that all other occurrences are false.

In the discussion above,

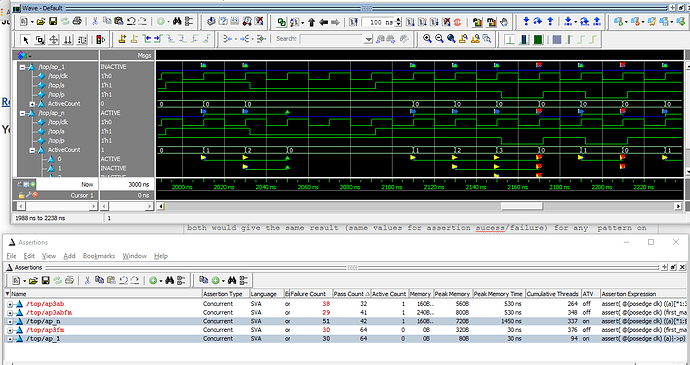

ap3ab: assert property(a[*1:3] ##1 b |-> p);

ap3abfm: assert property(first_match(a[*1:3] ##1 b) |-> p);

both these assertions are not same due to first_match. For ap3ab to succeed, all the threads in attempt need to succeed (vacuously or nonvacuouslys) while in ap3abfm, one you get one match, assertion succeeds and others threads need not succeed. Is that correct?

[Ben] correct, except that it is more correct to say that all other threads are not tested.

Also if the assertion a1 is in initial block, it will start only one attempt at first clock. Is this understanding correct?

[Ben] Correct.

Ben Cohen

http://www.systemverilog.us/ ben@systemverilog.us

- SVA Handbook 4th Edition, 2016 ISBN 978-1518681448

// For 10% discount, use code 45KJT5GN @ https://www.createspace.com/5810350

- A Pragmatic Approach to VMM Adoption 2006 ISBN 0-9705394-9-5

- Using PSL/SUGAR for Formal and Dynamic Verification 2nd Edition, 2004, ISBN 0-9705394-6-0

- Real Chip Design and Verification Using Verilog and VHDL, 2002 isbn 0-9705394-2-8

- Component Design by Example ", 2001 ISBN 0-9705394-0-1

- VHDL Coding Styles and Methodologies, 2nd Edition, 1999 ISBN 0-7923-8474-1

- VHDL Answers to Frequently Asked Questions, 2nd Edition ISBN 0-7923-8115